将数据转换器IP集成到系统芯片简化设计技术

为了满足苛刻性能和快速运行要求,今天的系统,从通讯接口到高品质图像视频和多媒体系统,各种消费类应用广泛采用了数字信号处理技术。数据转换器成为现实世界模拟信号与数字域之间的接口。因此,数据转换器是完整信号处理链上的重要组成部分,而信号处理是每台消费电子设备上不可或缺的一部分。

尽管数据转换器设计复杂,但IP厂商能够为系统芯片(SoC)设计师提供几乎可以满足任何系统要求的数据转换器。此外,为了提供适合系统芯片集成的数据转换器,Synopsys等知名的数据转换器IP厂商采用了尖端的电路和架构技术,使它们在严苛的系统芯片环境中仍然坚固耐用。这些电路和架构技术(不在本文讨论范围之内)可以免除大系统芯片中常见的衬底和电源噪声影响,以及对制程、温度和电压变化表现稳定。

不过,为了实现数据转换器IP性能最大化,系统芯片设计师必须应对将数据转换器与系统芯片集成的挑战,避免危害整个系统性能的缺陷。

数据转换器IP集成之所以会被认为错综复杂,其原因是它要求精心的手动布局布线。但是,通过深入了解影响性能的潜在问题,系统芯片设计师可以具备成功集成达到预期性能的所有技术手段。

本文系统地介绍了12种简化设计技术,这些技术解决了系统集成中的所有常见问题,有助确保在系统芯片中成功集成高性能数据转换器。

数据转换器基础知识

采用最适合系统芯片终端应用的性能、速度和功耗要求的架构与配置,可以选择两种类型数据转换器,即模拟-数字转换器(ADC)和数字-模拟转换器(DAC)。

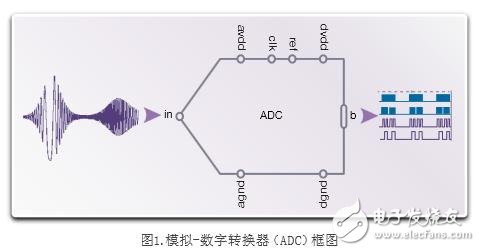

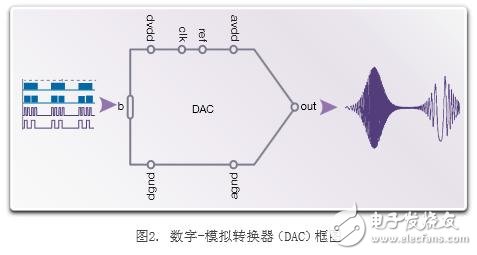

从物理集成的角度来看,两种数据转换器的信号接口相似,只不过ADC是将模拟输入信号转换成数字输出信号(图1),而DAC是将数字输入信号转换成模拟输出信号(图2)。

△模拟输入(in)/输出(out)信号有差分传输和单端传输方式,可有一个、两个或两个以上的通道;

△数字输出/输入(b)信号是模拟输入/输出信号的数字表现形式;

△参考电压可由内部基准电压源或外部输入;

△转换时钟(clk)可由内部锁相环驱动,或是由芯片外部提供;

△可提供电源和接地电源连接,包括模拟电源(avdd)、数字电源(dvdd)、模拟接地(agnd)和数字接地(dgnd)

成功的IP集成技术

第三方数字转换器IP在设计过程中考虑到了系统芯片集成和IP运行简单顺畅,没有障碍。但是,随意集成数据转换器可能造成系统性能变差。下面四部分将介绍几种有助确保IP集成成功的简单技术。

1. 首先在系统芯片上做合适的布局

系统芯片其他逻辑块产生的过大噪声会进入数据转换器继而影响其性能。为确保数据转换器与其他逻辑块很好地隔离,物理集成过程的第一步是在系统芯片中合理确定数据转换器的位置。

技术1:在活跃逻辑(攻击者)和模拟模块(受害者)之间保持一定距离

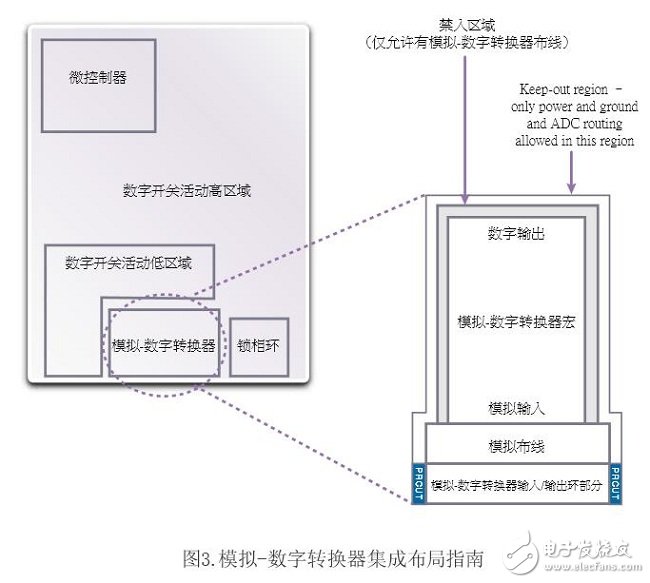

对于普通的模拟-数字转换器,采用这一技术可按照图3中的四个步骤进行操作:

1. 将数据转换器(如模拟-数字转换器)远离数字开关电路;

2. 数据转换器数字接口朝向芯片噪声较大区域,而模拟接口朝向芯片较安静区域;

3. 将时钟源(如锁相环)尽可能靠近数据转换器;

4. 如果数据转换器临近区域有数字开关走线或逻辑块,请设立一个禁入区域

(即没有金属、晶体管或有源区的区域),以便将数据转换器与逻辑块或布线隔离开。

技术2:数据转换器靠近模拟I/O焊盘

进入模拟-数字转换器输入的任何噪声或不需要的信号将被转换器视为"真"信号,继而出现在数字输出中。模拟-数字转换器能够区分的最小电压(用最低有效位(LSB)表示)决定数据转换器的准确度,也是模拟-数字转换器最大摆幅(FS)及其分辨率(N)的函数(如以下方程所示)。以0.5V峰-峰最大输入摆幅的12位单端模拟-数字转换器为例,最低有效位范围很小,仅为 122.1μV。

LSB = FS/2N

在如此高的准确度要求下,如果转换的数字信号(攻击者)电容耦合(串扰)到模拟-数字转换器输入(受害者),数字输出信号中耦合的攻击信号的频谱含量可能会超出模拟-数字转换器的噪声本底值,从而影响系统性能(频谱纯度)。

同样,串扰数字-模拟转换器输出对系统性能产生相似的影响,即转换的数字信号电容耦合到数字-模拟转换器输出可以生成超出数字-模拟转换器噪声本底值的频谱含量。

采用差分输入的模拟-数字转换器,或是采用差分输出的数字-模拟转换器,都具有较强的抗共模噪声干扰能力,因为攻击者均衡地耦合到正负差分信号。为充分利用这种高抗噪声干扰能力,使用这些数据转换器应同时采用

- 数据转换器中的DDC和DUC通道如何工作?(09-13)

- 将音频编解码器植入28nm高级移动多媒体芯片系统(10-18)

- 专家支招:如何快速解决隔离FPGA设计中的错误(07-15)

- 太阳能发电技术与绿色照明(09-10)

- 一种消防应急灯具专用控制芯片的设计(11-02)

- 基于以太网的可视对讲系统应用(08-30)