专家支招:如何快速解决隔离FPGA设计中的错误

如果您的FPGA设计无法综合或者没能按预期在开发板上正常工作,原因往往不明,要想在数以千计的RTL和约束源文件中找出故障根源相当困难,而且很多这些文件还可能是其他设计人员编写的。考虑到FPGA设计迭代和运行时间的延长,设计人员应该在设计流程的早期阶段就找出可能存在的诸多错误,并想方设法重点对设计在开发板上进行验证。

在特定条件下采用更智能的技术来隔离特定错误,找到问题电路的源头并渐进式修复错误,这很重要。为了节省时间,您可以对时钟、约束和模块级接口进行初步设置检查以确保符合设计规范,这样就不必在综合与布局布线(P&R)时浪费大量时间。

Synopsys 公司的Synplify Premier 和Synplify Pro FPGA设计工具以及Identify RTLDebugger 等产品能帮助设计人员完成上述工作。这些工具的特性使得设计人员能快速隔离错误,有效缩短运行时间,并减少开发板启动所需的迭代次数。

精确找到开发板上的问题

如果开发板出现明显的功能性错误,要缩小查找问题根源的范围可能会相当困难。为了进行设计调试,我们应当创建附加电路并保留某些节点,以便我们对设计运行时得到的数据进行探测、检查和分析。下面我们就看看如何用板级调试软件来查找错误。

按下列四步法并利用RTL调试器,您能精确查找问题,并对信号和关注的条件采样,然后将观察结果关联至原始RTL,从而将问题锁定在RTL规范或约束设置范围内。

第一步:指定探测。在RTL中明确要监控哪些信号和条件。在此要声明您所感兴趣的观察点(要观察的信号或节点)和断点(RTL控制流程声明,如IF、THEN 和CASE 等)。

第二步:通过探测构建设计。利用附加的监控电路——即用于根据您的监控要求捕捉并导出调试数据的智能内部电路仿真器(IICE)——对FPGA设计进行综合。

第三步:分析和调试。设计综合完成之后,运行设计并用RTL调试器观察数据。在开发板上运行测试时,观察点和断点共同触发数据采样,使您能在您所关注的非常明确的条件下观察并调试特定节点的电路的行为。您可将观察到的采样数据写入VCD 文件并将其关联到RTL。

第四步:渐进性修复错误(incrementaLfix)。一旦找到了错误所在,就可以通过分级、渐进式流程在RTL或约束中渐进地进行修复。

时序和功能性错误的可视检查

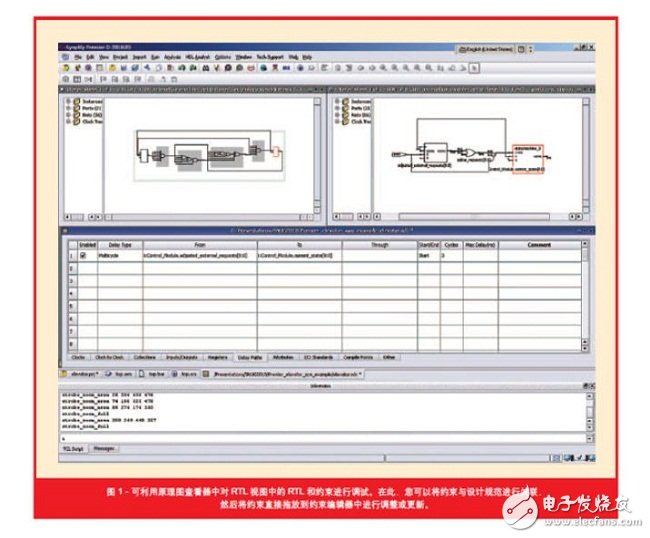

FPGA设计和调试工具还有一大优点,就是能显示RTL和网表级原理图。举例来说,具有互动调试功能的原理图查看器能够显示设计的RTL和网表原理图,便于您进行观察并将时序报告和VCD 数据(设计在开发板上运行时产生)关联至RTL源文件。查看器包含一个RTL视图,用来以图示的方式描述设计。该视图在综合RTL编译阶段后提供,由技术独立的加法器、寄存器、大型多路选择器和状态机等组件构成。通过RTL原理图,您可以交叉探测原始RTL,对不符合预定规范的设计进行调整,同时也可以探测到约束编辑器,从而更简便地更新和指定约束(图1)。

要将错误操作的源头追溯到RTL,您可以利用RTL调试器在RTL原理图上方实时插入观察到的操作数据。

原理图查看器包括一个网表级技术视图,用于显示综合后的实际设计实现情况。在HDLAnalyst 原理图查看器中,该视图基于查找表、寄存器和DSP slice 等基本的赛灵思器件原语。您可在原理图中对路径进行交叉探测,追溯到原始的RTL以及综合后和布局布线后的最终时序报告,以便分析和提高整体性能。

在FPGA中原型设计的ASIC 门控时钟结构并非FPGA实现中的必要环节,这会导致FPGA资源使用效率低下。解决该问题的有效办法就是用FPGA综合软件转换时钟。

大型设计的调试

在大型设计中探测所有信号是不可能,因为生成的数据量极为庞大,而且探测数据所需的额外调试逻辑也太大。片上调试方法的一个常见弊病是难以提前预测需要对哪些信号进行探测和监控。

一些调试软件通过分治法能够在一定程度上解决这个问题。利用多路复用的采样组,设计人员可以有选择性地进行采样并通过多路复用的路径和共享的IICE 在信号组之间切换。这种方法增加了可观察的信号和条件,而且不会增加数据存储要求。您可以即时切换感兴趣的信号组,不必花时间进行重新调整或重新综合新的设计。

不幸的是,在探测和采样数据时用使的调试IICE 逻辑会占用包括存储器BRAM 在内的芯片资源。您可在SRAM 存储卡中对IICE 采样数据进行片外存储,以减少片上BRAM 的使用。这种方法的另一个好处是能增加采样数据的深度。

我的设计无法综合

设计错误的出现可能导致无法实现有

- 将音频编解码器植入28nm高级移动多媒体芯片系统(10-18)

- 将数据转换器IP集成到系统芯片简化设计技术(04-27)

- 探索性数据分析(EDA)及其应用(10-18)

- 霍尼韦尔“互联网+医疗”解决方案亮相2016中华医院信息网络大会(04-27)

- 基于EDA或FPGA的IP保护的实现(09-16)

- 基于MC8051 IP核和FPGA的频率计设计(11-24)