基于ARM和FPGA的微加速度计数据采集系统设计

3.1 FPGA控制A/D芯片进行加速度计数据采集

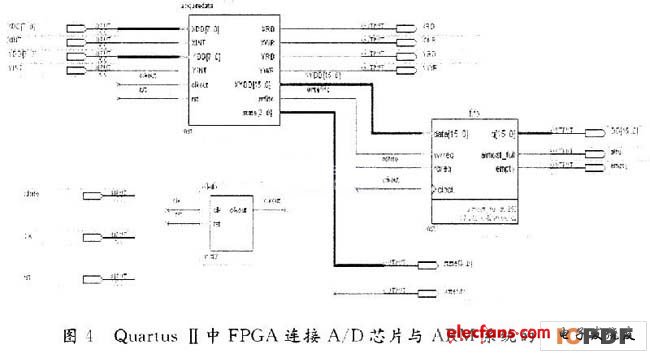

该加速度计是利用两路模拟电压输出来反映加速度值的大小,当加速度值为O时输出电压为1.50 V,电压输出灵敏度为150 mV/g,A/D转换器模拟输入电压范围为VCC±0.1 V,低于VREF- +(1/2)LSB或高于VREF+ -(1/2)LSB的模拟输入电压分别转换为00000000或1111111,系统中所加电压分别为VCC=VREF+=5 V,VREF-=GND=O V。TLC0820可通过MODE的设置工作在只读和读写两种方式。当MODE为低时,转换器为只读方式。在这种方式中,作为输出,且作为准备输出端;同时。当为低时,亦为低,表明器件忙,转换器在的下降沿开始转换,经过不到2.5μs转换完成,此时下降.为高阻,数据输出也由高阻变为有效的数据端,当数据读出后,变高,返回高,数据输出端返回到高阻态。当MODE为高时,转换器为读/写方式,作为写输出端。当和为低时,转换器开始测量输入信号,大约600 ns后返回高,转换器完成转换,在读写方式中,在上升沿开始转换。该实验采用读写方式来控制A/D芯片来读取加速度计的值,所需的控制信号由FPGA输出,相关的逻辑控制采用Verilog硬件描述语言进行编写,图4为QuartusⅡ中FPGA连接A/D芯片与ARM系统的顶层模块图。

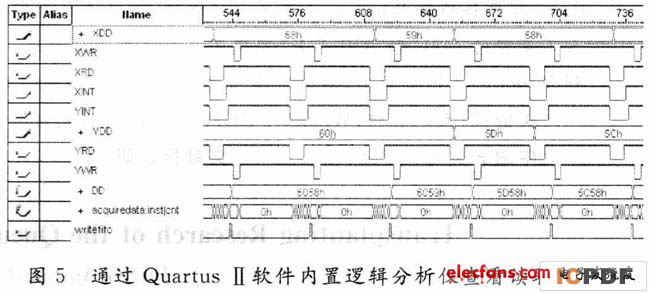

由A/D转换输出转换后的8位数字信号,可以从QuartusⅡ内置的逻辑分析仪中读取,图5为通过QuartusⅡ软件内置逻辑分析仪查看读取数据值的截图。从图5中可以看出在读写方式中,在WR/RDY的上升沿开始启动转换,到INT的下降沿转换完成,转换时间可通过时间标尺计算出来,为24×40=960 ns,之后就可以通过RD的上升沿开始读取转换后的数据到数据总线中,如图5中的XDD以及YDD。因为单片机的处理速度一般都低于A/D转换芯片的速度,故将XDD与YDD的数据存储到FPGA中的FIFO中,FIFO便起到数据缓冲的作用,以备接下来单片机对数据进行读取。

3.2 ARM系统接收FPGA数据

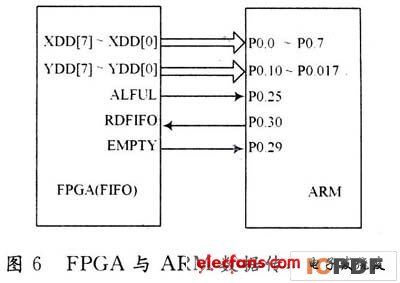

图6为FPGA与ARM相连接部分的传输接口框图。ARM系统主要控制数据采集的启动和采集结束后对数据的显示和存储,在数据采集的过程中,ARM处理器系统读取FPGA中的数据,实际上是读取FIFO中的数据。FIFO的容量可以通过软件进行设置,它有两个状态显示信号,分别为ALFUL和EMPTY,ALFUL是指FIFO接近满,当ALFUL从低电平变为高电平后,ARM单片机系统就可以发送RDFIFO信号来读取FIFO中的数据输出端口的数据,当FIFO中的EMPTY信号从低电平变为高电平,表明FIFO中已无数据可读,ARM单片机就开始等待ALFUL的跳变进行下一次的读取。

3.3 加速度数据显示和存储

由ARM系统采集到的数据可通过串口线发送到上位机进行实时显示,也可以通过模拟IDE通信协议储存到IDE硬盘中。LPC2210通过串口线与上位机进行通信主要是应用ARM芯片LPC2210中的通用异步接收/发送装置UART0,而使用LPC2210的通用可编程I/O口,可以模拟产生IDE硬盘的读写时序,实现对存储设备的读写操作。这样可以实现加速度数据的显示和存储。

4 结语

这里介绍一种MEMS器件微加速度计的数据采集设计方案,结合当前应用广泛的处理芯片ARM和FPGA,给出了一种配置灵活、通用性强的数据采集方案。实验中可准确采集美新加速度计MXR6150G/M的加速度信号,采集到的信号既可以在上位机实时显示,又可以存储在IDE接口硬盘中,达到了数据显示和存储的目的。(

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)