基于DSP的阵列声波信号采集与处理系统的设计

引言

随着传感器由过去的单个变为阵列结构,仪器要处理的信号也由过去单一的参数信号变为复杂的图像信号,同时,对信号的采集与处理也变得越来越复杂,研制一种阵列声波信号采集与处理系统,并进而开发出一种阵列声波测井仪,成为目前我国石油测井仪器发展的迫切需要。为此本文设计了一套基于DSP的阵列声波信号采集与处理系统,此系统将作为正在研制的阵列声波测井仪中的一部分,应用于油田勘探中。

系统总体方案设计

阵列声波测井仪由声系、电子线路和钢外壳组成。声系在最下端,由发出声波的发射晶体和接收声波并把其转换成电信号的传感器阵列组成。电子线路分为供电模块、主CPU模块和采集模块。其中,主CPU模块是阵列声波测井仪的控制部分,它一方面把地面部分传给采集模块和声系的参数传给采集模块和声系,另一方面把采集模块传上来的数据传给地面部分。采集模块即为阵列声波采集与处理系统,它的一端接声系的传感器阵列,另一端接主CPU,主要功能为在主CPU的控制下把前端传感器阵列传过来的信号采样、数字化并进行一系列的处理,然后把处理结果上传给主CPU。

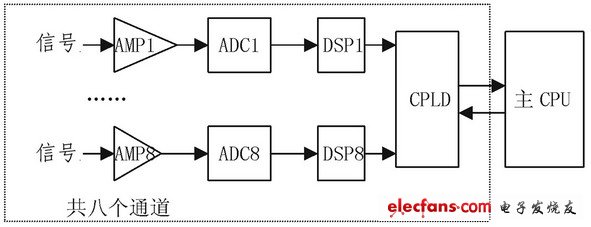

根据阵列声波采集与处理系统的性能要求和可靠性与低功耗设计原则,本设计决定采用以DSP芯片为核心的八通道实现方案,如图1所示。由于前端传感器阵列送来的数据信号比较微弱,要先由放大器对信号进行放大,同时此放大器也可以有效地减弱或消除后端ADC对前端模拟声波输入信号的影响。放大器之后是ADC,从放大器到DSP形成一个采集与处理的通道,系统中这样的通道共八个。而图1中的CPLD是系统的控制逻辑部分。此外,考虑到系统可靠性和实时性的要求,本系统设计成每个通道都有一个DSP处理器而不是八个通道共用一个DSP处理器。

图1 阵列声波信号采集与处理系统总体结构示意图

DSP设计

DSP芯片

由于整个阵列声波测井仪的其它芯片均为+5V供电,阵列声波采集与处理系统作为测井仪中的一部分,如果所选DSP芯片不是+5V供电,则需用电源转换芯片进行电压转换,这不仅使电路变得复杂,而且也不利于系统性能提高。所以本设计选用了TI公司的DSP芯片—TMS320C542(以下简称C542)。

C542除具有TMS320C54x的一般优点外,其单周期定点指令执行时间为25ns,运行速度相对较高,能够完成本系统采集与处理功能;且带有一个 BSP自动缓冲串口和一个TDM时分复用串口,两者都可用作SP标准同步串口。此外,无论是内核还是I/O引脚工作电压均为+5V,所以使用时不需电压转换芯片。

自举加载设计

传统DSP系统程序代码的引导装载多以并行EPROM作为应用程序的存储器方式,其最大弊端在于EPROM不支持在线擦写,这会对系统的调试带来很大的不便,特别是对于表贴封装的存储器,此方法基本不可用。

在本系统的设计中,采用了可以在线擦写的FLASH代替EPROM作为程序代码的存储器。因而从根本上克服了传统方法在系统调试上带来的诸多不便,对表贴封装的存储器尤为适用。调试过程中,直接将程序代码通过C542写入FLASH中,重新上电后C542即可按照FLASH的方式执行Bootloader 操作,极大的降低了硬件系统调试的难度。

本系统采用8位并行加载。C542复位期间检查MP/MC引脚是否为低电平,若不是,则从外部程序存储器0FF80h起执行用户程序;若是,则从片内 ROM的0FF80h起执行程序。启动制造商在ROM的自举加载器程序时,首先应进行初始化,然后检查INT2引脚,若有效,则从HPI-RAM自举加载;若无效,则使I/O口选通信号IS为低电平,从地址为0FFFFh的I/O口读入自举程序选择字(BRS)。BRS的低8位决定了自举加载的方式,若 BRS的低2位为01,则为8位并行加载,然后自举加载器依据FLASH的地址(BRS中的高6位 + 0000000000)就可读取自举表了。自举加载器将FLASH中的程序代码全部送到程序存储器之后,立即转移到目的地址,并开始执行程序代码。

本设计中FLASH芯片选用的是AMD公司的Am29F010,该芯片容量为1Mbit。因为C542只能寻址64K 地址,所以Am29F010的A16引脚接地。

DSP在线加载系统的硬件设计如图2所示。设计时没有让DS直接接CE,而是先让A14、A15分别接一个非门,这两个非门的输出端和IS一起接到一个或门上,此或门的输出端和DS一起接一个与门,与门的输出端再接CE。这样设计使Am29F010的48K至64K地址空间成为数据和I/O复用空间,自举加载时可从Am29F010的地址为0FFFFh的I/O口读入自举程序选择位。

图2 DSP在线加载硬件设计图

ADC设计

根据本系统对ADC分辨率为16位、转换速率大于125KSPS、低功

DSP 相关文章:

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于紫外检测法的智能型特高压验电器系统(03-17)

- 单一DSP控制两套三相逆变器的实现(08-31)

- 基于DSP生成SVPWM在逆变电源中的应用(11-09)

- DSP的大功率开关电源的设计方案(12-01)

- DSP处理器电源方案设计(02-08)