玩转赛灵思Zedboard开发板(5):基于AXI Lite总线的从设备IP设计

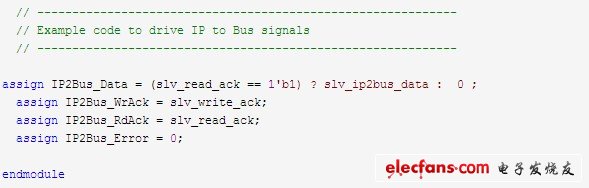

on the IP2Bus_Data bus is deemed valid at the rising edge of the Bus2IP_Clk and IP2Bus_RdAck asserted high by the user logic.

接下来需要使用需要使用BFM (Bus Functional Models, 总线功能模型)对外设进行仿真。本例IP很简单,不要使用。

最后,需要选择HDL类型、ISE工程支持和软件驱动模板。因为我比较习惯使用verilog,因而使用verilog模板。需要说明的是,IP接口仍然是VHDL编写,只是用户逻辑改用verilog。如果不需要使用软件驱动模板的话,可以不选上。这里选上了,但是后续编程的时候我并没有用。

最后给出了外设的信息summary。支持,my_axi_ip"外壳"基本完成。后续我们只需要对user_logic进行编写,并修改元件引脚即可。

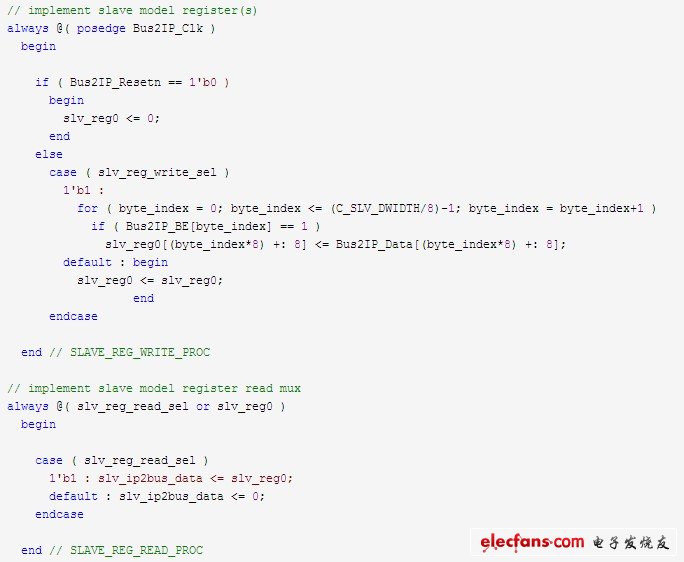

2、编写IP

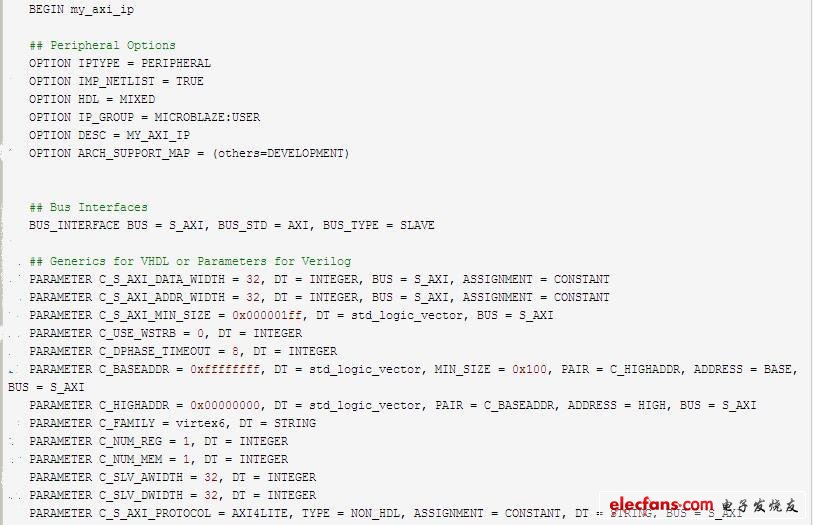

修改.mpd文件,在目录

Lab4\pcores\my_axi_ip_v1_00_a\data\

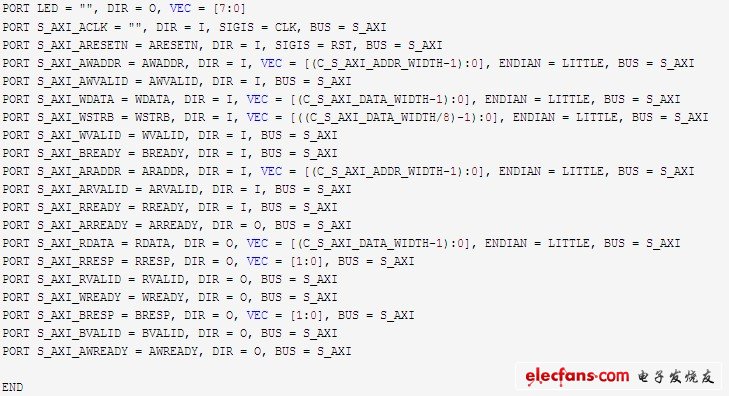

其中,第39行

PORT LED = "", DIR = O, VEC = [7:0]

是我们添加上的,表明我们为其添加了一个名为LED的端口,方向是输出,长度是8位。其他行代码为默认,不需要修改。

修改用户逻辑,在

Lab4\pcores\my_axi_ip_v1_00_a\hdl\verilog\user_logic.v

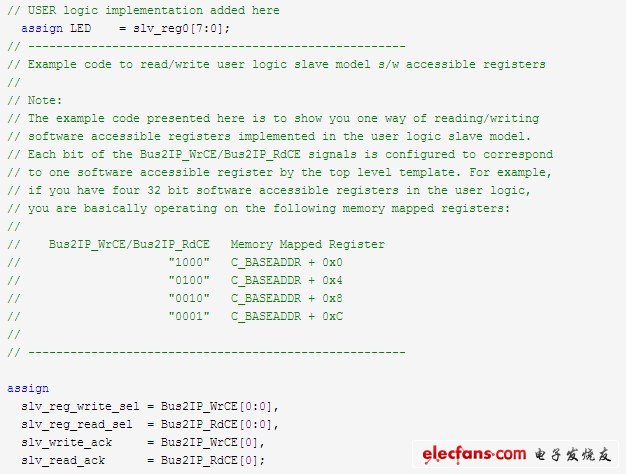

代码中57、86行

LED,

output [7:0] LED;

表明在用户逻辑中,定义了名为LED的端口,方向是输出,长度为8。

代码中119行

assign LED = slv_reg0[7:0];

表明将slv_reg0的低8位传递给输出端口LED。其实就是实现了数据寄存器的值作用到输出端口的功能。

需要将用户逻辑和IPIF连接上,需要完成user_logic的例化

Lab4\pcores\my_axi_ip_v1_00_a\hdl\vhdl\my_axi_ip.vhd

1 ------------------------------------------------------------------------------

2 -- my_axi_ip.vhd - entity/architecture pair

3 ------------------------------------------------------------------------------

4 -- IMPORTANT:

5 -- DO NOT MODIFY THIS FILE EXCEPT IN THE DESIGNATED SECTIONS.

6 --

7 -- SEARCH FOR --USER TO DETERMINE WHERE CHANGES ARE ALLOWED.

8 --

9 -- TYPICALLY, THE ONLY ACCEPTABLE CHANGES INVOLVE ADDING NEW

10 -- PORTS AND GENERICS THAT GET PASSED THROUGH TO THE INSTANTIATION

11 -- OF THE USER_LOGIC ENTITY.

12 ------------------------------------------------------------------------------

13 --

14 -- ***************************************************************************

15 -- ** Copyright (c) 1995-2012 Xilinx, Inc. All rights reserved. **

16 -- ** **

17 -- ** Xilinx, Inc. **

18 -- ** XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION "AS IS" **

19 -- ** AS A COURTESY TO YOU, SOLELY FOR USE IN DEVELOPING PROGRAMS AND **

20 -- ** SOLUTIONS FOR XILINX DEVICES. BY PROVIDING THIS DESIGN, CODE, **

21 -- ** OR INFORMATION AS ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, **

22 -- ** APPLICATION OR STANDARD, XILINX IS MAKING NO REPRESENTATION **

23 -- ** THAT THIS IMPLEMENTATION IS FREE FROM ANY CLAIMS OF INFRINGEMENT, **

24 -- ** AND YOU ARE RESPONSIBLE FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE **

25 -- ** FOR YOUR IMPLEMENTATION. XILINX EXPRESSLY DISCLAIMS ANY **

26 -- ** WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE **

27 -- ** IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR **

28 -- ** REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF **

29 -- ** INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS **

30 -- ** FOR A PARTICULAR PURPOSE. **

31 -- ** **

32 -- ***************************************************************************

33 --

34 ------------------------------------------------------------------------------

35 -- Filename: my_axi_ip.vhd

36 -- Version: 1.00.a

37 -- Description: Top level design, instantiates library components and user logic.

38 -- Date: Tue Oct 09 18:28:06 2012 (by Create and Import Peripheral Wizard)

39 -- VHDL Standard: VHDL'93

40 ----------------