ARM Cortex-M 处理器家族介绍和比较

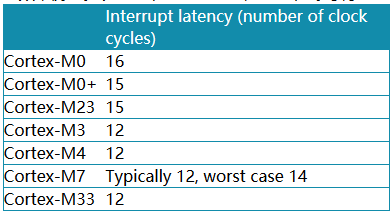

表 8: 零等待内存系统条件下的中断延迟比较

事实上,真正的中断延迟受到内存系统等待状态的影响。例如,许多运行频率超过100Mhz的微控制器搭配的是非常慢的Flash存储器(例如30到50MHz)。虽然使用了Flash访问加速硬件来提高性能,中断延迟仍然受到Flash存储系统等待状态的影响。所以完全有可能运行在零等待内存系统Cortex-M0/M0+系统比Cortex-M3/M4/M7有更短的中断延迟。

当评估性能的时候,不要忘记把中断处理程序的执行时间考虑在内。某些8位或者16位处理器架构可能中断延迟很短,但是会花费数倍的时钟周期完成中断处理。非常短的中断响应时间和很短的中断处理时间才是实际有效的。

6调试和跟踪特性

6.1调试和跟踪特性简介

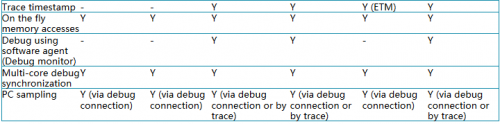

不同Cortex-M处理器之间有若干区别。总结在表9中。

表9: 调试和跟踪特性比较

Cortex-M处理器的调试架构是基于ARM CoreSight调试架构设计的,它是个非常容易扩展的架构,支持多处理器系统。

表9列出的是典型设计需要考虑的。在CoreSight架构下,调试接口和跟踪接口模块是和处理器分离的。因此你采用的设备的调试和跟踪连接和表9的可能不一样。也可能通过添加一些额外的CoreSight调试组件来增加一些调试特性。

6.2Debug connections调试接口

调试接口可以让调试者实现

-访问控制调试和跟踪特性的寄存器。

-访问内存空间。对Cortex-M系列处理器,及时当处理器运行时也可以执行内存空间访问。这被称作实时内存访问。

-访问处理器核心寄存器。这只能当处理器停止的时候才可以操作。

-访问Cortex-M0处理器中微跟踪缓存(MTB)生成的跟踪历史记录。

另外,调试接口也会用作:

-Flash 编程

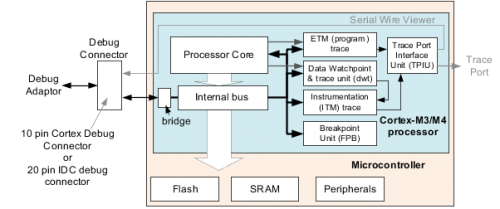

Cortex-M系列处理器可以选择传统的4到5个引脚(TDI, TDO, TCK, TMS 和可选的 nTRST)的JTAG接口,或者选择新的只需要两个引脚的串行调试协议接口,串行调试接口对有限数目引脚的设备是非常适合的。

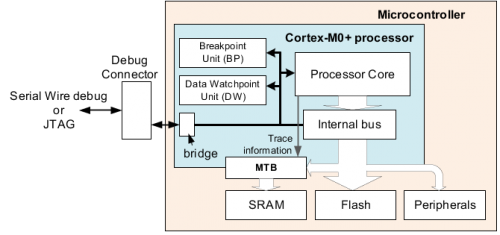

图 10: 串口线或者JTAG调试接口allows access to processor’s debug features and memory space including peripherals

串行线调试协议接口可以处理JTAG支持的所有特性,支持奇偶校验。串行调试协议被ARM工具厂商广泛的采用,许多调试适配器两种协议都支持,串行线型号共享调试接口上TCK和TMS针脚。

6.3跟踪接口

跟踪接口让调试者可以在程序执行时实时的(很小的延时)收集程序运行的信息。收集的信息可以是Cortex-M3/M4/M7/M33支持的嵌入式跟踪单元(ETM)生成的程序指令流信息(指令跟踪),可以是数据跟踪单元(DWT)生成的数据/事件/性能分析信息,或者是软件控制数据跟踪单元(ITM)生成的信息。

有两种类型的跟踪接口可用:

-跟踪端口(Trace port)– 多个数据线加上时钟信号线。比SWV有更高的跟踪带宽,可以支持SWV的所有跟踪类型加上指令跟踪。Cortex-M3/M4/M7或者 Cortex-M33的设备上,跟踪端口通常有4个数据线和一个时钟线。(图11)

-串行监视器(SWV)– 单引脚线跟踪接口,可以选择性的支持数据跟踪,事件跟踪,性能分析和测量跟踪。(图 12)

图 11: Trace port 支持指令跟踪和其他跟踪功能必要的带宽

跟踪接口提供了在处理器运行的时候获取大量有用信息的能力。例如嵌入式跟踪单元(ETM)可以获取指令运行历史记录,数据跟踪单元(ITM)让软件产生消息(例如,通过printf)并利用Trace接口获取。另外,Cortex-M3/M4/M7/M33支持数据跟踪单元(DWT)模块。

-可选的数据跟踪:内存地址的信息(例如,地址,数据和时间戳的组合)可以在处理器访问这个地址的时候采集

-性能分析跟踪:CPU在不同操作任务使用的时钟周期数(例如,内存访问,休眠)

-事件跟踪:提供服务器响应的中断/异常的运行时间和历史

图 12: Serial wire viewer 提供了低成本,少引脚的跟踪方案

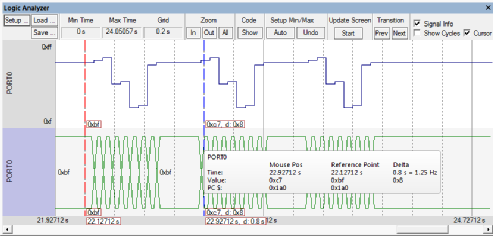

这些跟踪特性被各种工具厂商广泛采用,采集的信息也被以各种方式直观的展现出来。例如DWT获取的数据可以在Keil µVision调试器中以波形的方式展现出来(Keil微控制器开发工具的一部分)如图 13所示。

Figure 13: Keil µVision 调试器的逻辑分析器

虽然Cortex-M0 和 Cortex-M0+不支持跟踪接口,Cortex-M0+支持叫做微跟踪缓存的特性(MTB,图14)。MTB让用户分配一小块系统SRAM作为存储指令的缓存,通常设置为循环缓存,这样可以抓取最新的指令执行历史并在调试器上显示出来。

这个MTB跟踪特性也被Cortex-M23 and Cortex-M33支持。

图 14: Cortex-M0+/M23/M33 的MTB提供了低成本指令跟踪方案

7基于Cortex-M处理器的产

- 分析:2011年商用PC市场发展情况乐观(03-01)

- 富士通半导体与ARM签署全面授权协议(03-07)

- ARM手机芯片市场份额已超90% 英特尔倍感压力(03-17)

- 中国正探寻如何快速进驻HPC芯片领域(03-23)

- 美国国家半导体推出10款全新SolarMagic IC芯片 (05-03)

- IDC:中国一季度平板电脑出货量达86万台(07-20)