ARM Cortex-M 处理器家族介绍和比较

2.6Cortex-M23指令集

Cortex-M23的指令集是基于ARMv8-M的Baseline子规范,它是ARMv6-M的超集。扩展的指令包括:

·硬件除法指令

·比较和跳转指令,32位跳转指令

·支持TrustZone安全扩展的指令

·互斥数据访问指令(通常用于信号量操作)

·16位立即数生成指令

·载入获取及存储释放指令(支持C11)

在某些情况下,这些增强的指令集可以提高处理器性能,并且对包含多个处理器的SoC设计有用(例如,互斥访问对多处理器的信号量处理有帮助)

2.7I Cortex-M33指令集

因为Cortex-M33设计是非常可配置的,某些指令也是可选的。例如:

·DSP指令(Cortex-M4 和Cortex-M7支持的)是可选的

·单精度浮点运算指令是可选的,这些指令是基于FPv5的,并且比Cortex-M4多几条。

: Cortex-M33也支持那些ARMv8-M Mainline引入的新指令:

·支持TrustZone安全扩展的指令

·载入获取及存储释放指令(支持C11)

2.8指令集特性比较总结

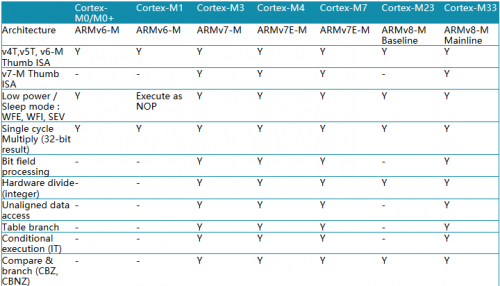

ARMv6-M, ARMv7-M 和 ARMv8-M架构有许多指令集功能特点, 很难介绍到所有的细节。但是,下面的表格(表4)总结了那些关键的差异。

表 4: 指令集特性总结

Cortex-M处理器指令集的最重要的特点是向上兼容。Cortex-M3的指令是Cortex-M0/M0+/M1的超集。所以,理论上讲,如果存储空间分配是一致的,运行在Cortex-M0/M0+/M1上的二进制文件可以直接运行在Cortex-M3上。同样的原理也适用于Cortex-M4/M7和其他的Cortex-M处理器;Cortex-M0/M0+/M1/M3支持的指令也可以运行在Cortex-M4/M7上。

虽然Cortex-M0/M0+/M1/M3/M23处理器没有浮点运算单元配置选项,但是处理器仍然可以利用软件来做浮点数据运算。这也适用于基于Cortex-M4/M7/M33但是没有配置浮点运算单元的产品。在这种情况下,当程序中使用了浮点数,编译工具包会在链接阶段插入需要的运行软件库。软件模式的浮点运算需要更长的运行时间,并且会略微的增加代码大小。但是,如果浮点运算不是频繁使用的,这种方案是适合这种应用的。

3架构特性

3.1编程模型

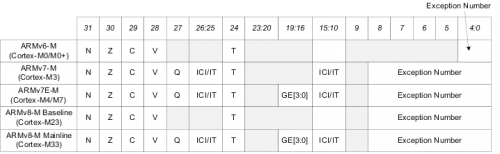

Cortex-M处理器家族的编程模型是高度一致的。例如所有的Crotex-M处理器都支持R0到R15,PSR, CONTROL 和 PRIMASK。两个特殊的寄存器- FAULTMASK 和 BASEPRI-只有Cortex-M3, Cortex-M4, Cortex-M7 和 Cortex-M33支持;浮点寄存器组和FPSCR(浮点状态和控制寄存器)寄存器,是Cortex-M4/M7/M33可选的浮点运算单元使用的。

图 5: 编程模型

BASEPRI寄存器允许程序阻止指定优先级或者低的优先级中断和异常。对ARMv7-M来说这是很重要的,因为Cortex-M3, Cortex-M4, Cortex-M7 和 Cortex-M33有大量的优先级等级,而ARMv6-M 和 ARMv8-M Baseline只有有限的4个优先等级。FAULTMASK通常用在复杂的错误处理上(查看章节3.4)

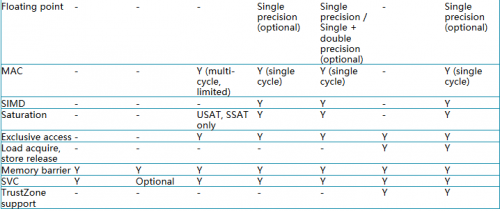

非特权级别的实现对ARMv6-M处理器是可选的,对ARMv7-M 和ARMv8-M处理器一直支持的。对Cortex-M0+处理器,它是可选的, Cortex-M0 and Cortex-M1不支持这个功能。这意味着在各种Cortex-M处理器的CONTROL 寄存器是稍微不同的。FPU的配置也会影响到CONTROL寄存器,如图6所示。

图 6: CONTROL 寄存器

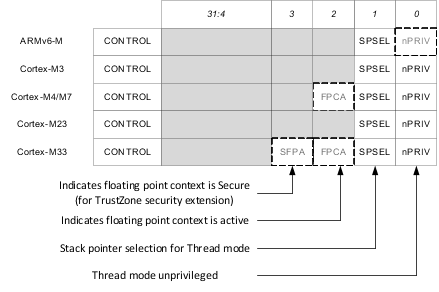

另外一个编程模型之间的不同是PSR寄存器(程序状态寄存器)的细节。所有的Cortex-M处理器,PSR寄存器都被再分成应用程序状态寄存器(APSR),执行程序状态寄存器(EPSR)和中断程序状态寄存器(IPSR)。 ARMv6-M 和 ARMv8-M Baseline系列的处理器不支持APSR的Q位和EPSR的ICI/IT位。ARMv7E-M系列 ( Cortex-M4, Cortex-M7) 和ARMv8-M Mainline (配置了DSP扩展的Cortex-M33 )支持GE位。另外,ARMv6-M系列处理器IPSR的中断号数字范围很小,如图7所示。

图 7: PSR 差异

请注意Cortex-M的编程模型和ARM7TDMI等这些经典的ARM处理器是不一样的。除了寄存器组不同外,经典ARM处理器中"模式"和"状态"的定义与Cortex-M中的也是不同的。Cortex-M只有两个模式:线程模式(Thread)和管理者模式(Handler),并且Cortex-M处理器一直运行在Thumb状态(不支持ARM指令)

3.2异常处理模型和嵌套向量中断控制器NVIC

所有的Cortex-M处理器都包含了NVIC模块,采用同样的异常处理模型。如果一个异常中断发生,它的优先等级高于当前运行等级,并且没有被任何的中断屏蔽寄存器屏蔽,处理器会响应这个中断/异常,把某些寄存器入栈到当前的堆栈上。这种堆栈机制下,中断处理程序可以编写为一个普通的C函数,许多小的中断处理函数可以立即直接响应工作而不需要额外的堆栈处理花销。

一些ARMv7-M/ARMv8-M Mainline系列的处理器使用的中断和系统异常并不被ARMv6-M/ARMv8-M Baseline的产品支持,如图8. 例如,Cortex-M0, M0+ 和M1的中断数被限制在32个以下,没有调试监测异常,错误异常也只限于HardFault(错误处理细节请参看章节3.4)。相比之下,Cortex-M23, Cortex-M3, Cortex-M4 和Cortex-M7处理器可以支持到多达240个外围设备中断。Cortex-M33支持最多480个中断。

- 分析:2011年商用PC市场发展情况乐观(03-01)

- 富士通半导体与ARM签署全面授权协议(03-07)

- ARM手机芯片市场份额已超90% 英特尔倍感压力(03-17)

- 中国正探寻如何快速进驻HPC芯片领域(03-23)

- 美国国家半导体推出10款全新SolarMagic IC芯片 (05-03)

- IDC:中国一季度平板电脑出货量达86万台(07-20)