ARM Cortex-M 处理器家族介绍和比较

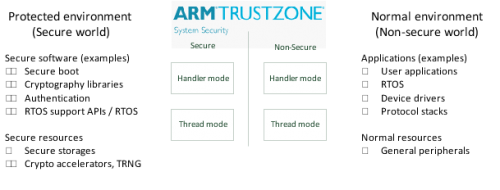

图 9: 安全状态和非安全状态的隔离

非安全状态的软件只能访问非安全状态的存储空间和外围设备,安全软件可以访问两种状态下的所有资源。

用这种方案,软件开发者可以用以往的方式开发非安全环境下的应用程序。同时,他们可以借助芯片厂商提供的安全通讯软件库执行安全物联网连接。并且即使运行在非安全环境的特权级的程序有漏洞,TrustZone安全机制可以阻止黑客控制整个设备,限制了攻击的影响,还可以实现系统远程恢复。此外,ARMv8-M架构也引入了堆栈边界检查和增强的MPU设计,促使额外安全措施的采用。

安全架构定义也扩展到了系统级别,每个中断都可以被设置为安全或者非安全属性。中断异常处理程序也会自动保存和恢复安全环境中的寄存器数据以防止安全信息泄露。所以,TrustZone安全扩展让系统能够支持实时系统的需求,为IoT应用提供了坚实的安全基础,并且容易让软件开发在此技术上开发应用程序。

TrustZone模块对Cortex-M23 and Cortex-M33处理器是可选的。关于ARMv8-M TrustZone更多的信息请查找The Next Steps in the Evolution of Embedded Processors for the Smart Connected Era。更多的TrustZone的资源请查看community.arm.com网站上的"TrustZone for ARMv8-M Community",

3.5错误处理

ARM处理器和其他架构的微控制器的一个区别是错误处理能力。当错误被检测到时,一个错误异常处理程序被触发去执行恰当的处理。触发错误的情况可能是:

·未定义的指令(例如,Flash存储器损坏)

·访问非法地址空间(例如,堆栈指针崩溃)或者MPU非法访问

·非法操作(例如,当处理器已经在优先级高于SVC的中断中试图触发SVC异常)

错误处理机制使嵌入式系统能够更快的响应各种问题。否则,如果系统死机了,看门狗定时需要非常长的时间重启系统。

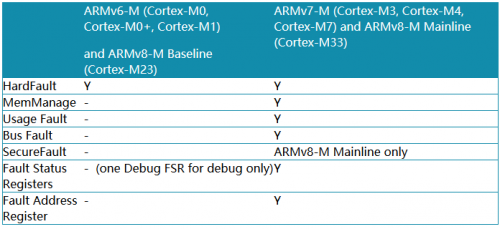

ARMv6-M架构中,所有的错误事件都会触发HardFault处理程序,它的优先级是-1(优先级比所有的可编程异常都高,但是仅低于非屏蔽中断NMI)。 所有的错误事件都被认为是不可恢复的,通常我们在HardFault处理程序中仅运行错误报告然后进一步触发自动复位。

ARMv8-M Baseline架构和ARMv6-M类似,只有一个错误异常(HardFault)。但是ARMv8-M Baseline的HardFault优先级可以是-1或者当实现了TrustZone安全扩展时优先级是-3.

ARMv7-M 和 ARMv8-M Mainline产品除了HardFault还有几个可配置的错误异常:

·Memmanage(内存管理错误)

·总线错误(总线返回错误的响应)

·用法错误(未定义指令或者其他的非法操作)

·SecureFault(只用ARMv8-M Mainline产品支持,处理TrustZone安全扩展中的安全非法操作)

这些异常的优先级可以编程改变,可以单独的打开和关掉。如果需要,它们也可以利用FAULTMASK寄存器把它们的优先级提高到和HardFault相同的级别。ARMv7-M 和 ARMv8-M Mainline产品还有几个错误状态寄存器可以提供关于触发错误异常事件的线索和错误地址的寄存器,用来确定触发这个错误异常的访问地址,使调试更加容易。

ARMv7-M 和 ARMv8-M Mainline产品子规范中额外的错误处理程序提供了灵活的错误处理能力,错误状态寄存器让错误事件的定位和调试更加容易。很多商业开发套件中的调试器已经内嵌了使用错误状态寄存器来诊断错误事件的功能。此外,错误处理程序可以在运行时做一些修复工作。

表 6: 错误处理特性比较总结

4系统特性

4.1低功耗

低功耗是Cortex-M处理器的一个关键优点。低功耗是其架构的组成部分:

·WFI和WFE指令

·架构级的休眠模式定义

此外,Cortex-M支持许多其他的低功耗特性:

·休眠和深度休眠模式:架构级支持的特性,通过设备特定的功耗管理寄存器可以进一步扩展。

·Sleep-on-exit模式:中断驱动的应用的低功耗技术。开启设置后,当异常处理程序结束并且没有其他等待处理的异常中断时,处理器自动进入到休眠模式。这样避免了额外的线程模式中指令的执行从而省电,并且减少了不必要的堆栈读写操作。

·唤醒中断控制器(WIC):一个可选的特性,在特定的低功耗状态,由一个独立于处理器的小模块侦测中断情况。例如,在状态保留功耗管理(SRPG)设计中,当处理器被关电的设计。

·时钟关闭和架构级时钟关闭:通过关闭处理器的寄存器或者子模块的时钟输入来省电

所有这些特性都被Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23 和 Cortex-M33支持。此外,各种低功耗设计技术被用来降低处理器功耗。

因为更少的电路,Cortex-M0 and Cortex-M0+处理器比Cortex-M3, Cortex-M4 和 Cortex-M7功耗低。此外,Cortex-M0+额外优化减少了程序存取(例如跳转备份)来保持系统层级的低功耗。

Cortex-M23没有Cortex-M0 和 Cortex-M0+那么小,但是在相同的配置下,仍然和Cortex-M0+能效一样。

由于更好性能和低功耗优化,在相同配置下,Cortex-M33比Cortex-M4能效比更好。

- 分析:2011年商用PC市场发展情况乐观(03-01)

- 富士通半导体与ARM签署全面授权协议(03-07)

- ARM手机芯片市场份额已超90% 英特尔倍感压力(03-17)

- 中国正探寻如何快速进驻HPC芯片领域(03-23)

- 美国国家半导体推出10款全新SolarMagic IC芯片 (05-03)

- IDC:中国一季度平板电脑出货量达86万台(07-20)