ARM Cortex-M 处理器家族介绍和比较

另外一个区别是可以使用的优先等级数量:

ARMv6-M 架构 - ARMv6-M支持2级固定的(NMI 和 HardFault)和4级可编程的(由每个优先等级寄存器的两个位表示)中断/异常优先级。这对大多数的微控制器应用来说足够了。

ARMv7-M 架构 - ARMv7-M系列处理器的可编程优先级等级数范围,根据面积的限制,可以配置成8级(3位)到256级(8位)。ARMv7-M处理器还有一个叫做中断优先级分组的功能,可以把中断优先级寄存器再进一步分为组优先级和子优先级,这样可以详细地制定抢占式优先级的行为。

ARMv8-M Baseline – 类似 ARMv6-M,M23也有2位的优先级等级寄存器。借助可选的TrustZone安全扩展组件,安全软件可以把非安全环境中的中断的优先等级转换到优先等级区间的下半区,这就保证了安全环境中的某些中断/异常总是比非安全环境中的优先级要高。

ARMv8-M Mainline – 类似于 ARMv7-M。 可以支持8到256个中断优先等级和中断优先级分组。还支持ARMv8-M Baseline具有的优先等级调整功能。

图 8: Cortex-M 处理器异常中断类型

所有的Cortex-M处理器在异常处理是都要依靠向量表。向量表保存着异常处理函数的起始地址(如图8所示)。向量表的起始地址由名为向量表偏移寄存器(VTOR)决定。

·Cortex-M0+, Cortex-M3 and Cortex-M4 processors: by default the vector table is located in the starting of the memory map (address 0x0). Cortex-M0+, Cortex-M3 and Cortex-M4: 向量表默认放在存储空间的起始地址(地址 0x0)。

·In Cortex-M7, Cortex-M23 and Cortex-M33 processors: the default value for VTOR is defined by chip designers. Cortex-M23 and Cortex-M33 processors can have two separated vector tables for Secure and Non-secure exceptions/interrupts. Cortex-M7, Cortex-M23 and Cortex-M33:VTOR的初始值由芯片设计者定义。Cortex-M23 and Cortex-M33处理器面向安全和非安全的异常/中断有两个独立的向量表。

·Cortex-M0 and Cortex-M1 does not implement programmable VTOR and vector table starting address is always 0x00000000. Cortex-M0 and Cortex-M1没有实现可编程的VTOR,向量表起始地址一直为0x00000000。

Cortex-M0+ 和 Cortex-M23处理器的VTOR是可选项。如果VTOR被实现了,向量表的起始地址可以通过设置VTOR来改变,这个功能对下列情况有用:

·重定位向量表到SRAM来实现动态改变异常处理函数入口点

·重定位向量表到SRAM来实现更快的向量读取(如果flash存储器很慢)

·重定位向量表到ROM不同位置(或者Flash),不同的程序运行阶段可以有不同的异常处理程序

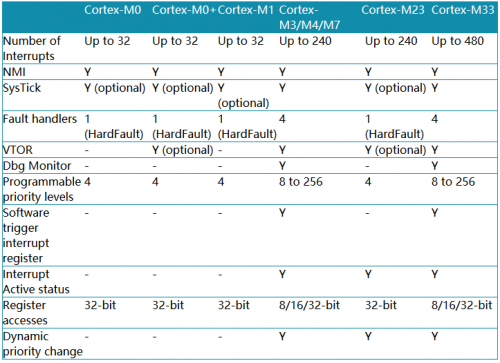

不同的Cortex-M处理器之间的NVIC编程模型也有额外的不同。差异点总结在表 5中:

表 5: NVIC 编程模型和特性差异

大部分情况下,对NVIC的中断控制特性的操作都是通过CMSIS-CORE提供的APIs处理的,他们在微控制器厂商提供的设备驱动程序库里。对Cortex-M3/M4/M7/M23/M33处理器,即使中断被使能了,它的优先级也可以被改变。ARMv6-M处理器不支持动态优先等级调整,当你需要改变中断优先等级是,需要暂时的关掉这个中断。

3.3操作系统支持特性

Cortex-M处理器架构在设计时就考虑到了操作系统的支持。针对操作系统的特性有:

·影子堆栈指针

·系统服务调用(SVC)和可挂起系统调用(PenSV)异常

·SysTick – 24位递减计时器,为操作系统的计时和任务管理产生周期性的异常中断

·Cortex-M0+/M3/M4/M7/M23/M33支持的非特权执行和存储保护单元(MPU)

系统服务调用(SVC)异常由SVC指令触发,他可以让运行在非特权状态的应用任务启动特权级的操作系统服务。可挂起系统调用异常在操作系统中像上下文切换这样的非关键操作的调度非常有帮助。

为了能把Cortex-M1放到很小的FPGA器件中,所有用来支持操作系统的特性对Cortex-M1都是可选的。对Cortex-M0, Cortex-M0+ 和Cortex-M23处理器,系统时钟SysTick是可选的。

通常,所有的Cortex-M处理器都支持操作系统。执行在Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23 和 Cortex-M33的应用可以运行在非特权运行状态,并且可以同时利用可选的存储器管理单元(MPU)以避免内存非法访问。这可以增强系统的鲁棒性。

3.4TrustZone安全扩展

近几年来, 物联网(IoT)成为了嵌入式系统开发者们的热门话题。IoT系统产品变得更加复杂,上市时间的压力也与日俱增。嵌入式系统产品需要更好的方案来保证系统的安全,但是同时又要方便软件开发者开发。传统的方案是通过把软件分成特权和非特权两部分解决的,特权级软件利用MPU防止非特权的应用访问包含安全敏感信息在内的的关键的系统资源。这种方案对一些IoT系统非常适合,但是在一些情况下,只有两层划分是不够的。特别是那些包含很多复杂特权级别的软件组件的系统,特权级的代码的一个缺陷就可以导致黑客彻底的控制这个系统

ARMv8-M架构包含了一个叫做TrustZone的安全扩展,TrustZone导入了安全和非安全状态的正交划分。

·普通应用是非安全态

·软件组件和安全相关的资源(例如,安全存储,加密加速器,正随机数发生器(TRNG))处在安全状态。

- 分析:2011年商用PC市场发展情况乐观(03-01)

- 富士通半导体与ARM签署全面授权协议(03-07)

- ARM手机芯片市场份额已超90% 英特尔倍感压力(03-17)

- 中国正探寻如何快速进驻HPC芯片领域(03-23)

- 美国国家半导体推出10款全新SolarMagic IC芯片 (05-03)

- IDC:中国一季度平板电脑出货量达86万台(07-20)