谈第二代异构计算,OpenPOWER有CAPI+FPGA不服来战

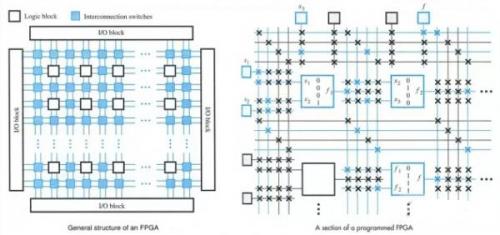

FPGA的内部主要是由用于实现硬件逻辑的逻辑块(LB,Logic Block)、负责LB互联的内部互联交换节点(IS,Interconnection Switch)以及负责输入输出的I/O Block组成,它们都是可编程的,而随着技术的进步,FPGA芯片里也越来越多的集成相关的固定器件与硬核(IP)电路,如乘法器、数字信号处理器(Digital Signal Processor)等,以进一步加速相关的运算,并完善相关的功能(比如I/O)

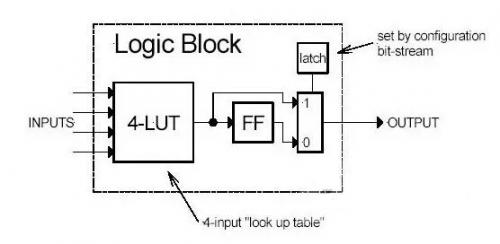

LB是FPGA内的基本逻辑单元,是FPGA可实现逻辑编程的基础,而在LB中最常用的逻辑编程器件就是查找表(LUT,Look Up Table,又称直译表),通过编程它可以实现输入与输出的直接对应关系,从而实现了输入与输出的硬逻辑,在应用时,直接根据输入的值,通过LUT给出相应的输出值。输入的组合根据输入端口数量而定,比如4个端口就可实现16种输入组合(2的4次方),而一个LB可以包含有多个LUT,实现更复杂的逻辑组合

FPGA的内部总体架构,主要是由实现硬件逻辑的逻辑块(LB)、负责LB互联的内部互联交换节点(IS)以及负责输入输出的I/O Block组成。由于几乎所有的逻辑电路都是通过不同门电路的组合来实现的,所以FPGA其实就是提供了数量众多的门电路,让用户用硬件描述语言(HDL,Hardware Description Language)自行设计它们各自的逻辑状态与相互之间的逻辑关系,从而让被编程的FPGA变成为某种专用芯片,所以说FPGA是ASIC的半成品,不无道理。

事实上,FPGA在早期的一个重要的用途就是为了更好的设计ASIC,毕竟等ASIC生产出来再实验的成本太高。而通过FPGA可以进行复杂的逻辑测试,来验证ASIC的设计,并通过可编程进行反复的优化。当逻辑优化到相当水平后,再以更为直接的逻辑实现方法形成ASIC电路,以达到更好的性能。随着FPGA自身的性能、能力与可实现逻辑的复杂度的不断提升,现在FPGA已经逐渐可以直接代替一些中等规模的ASIC来使用,并在整体功耗上,保持对CPU的明显优势。

在国内率先开发CAPI+FPGA加速卡解决方案的,恒扬科技股份有限公司大数据采集与分析产品经理张军,这样形容FPGA,"FPGA就是一张白纸,(最终的逻辑电路)想画什么完全由设计师决定,而 CPU等软件编程的器件就像铅笔画(已经有了框架),设计师是在上面涂色彩。" 事实上,FPGA可以实现怎样的能力,主要就取决于它所提供的门电路的规模。

现在主流的FPGA内部均采用了SRAM编程方式(SRAM本身就是一个逻辑部件可用于LUT,而SRAM晶体管可用于内部互联链路的选通组合),可以实现快速的硬件编程,并能无限次的重复使用。虽然SRAM的特性决定了关机后内部逻辑组合就会消失,但基于SRAM的编程在每次开机时都可以从外部的Flash芯片即时加载FPGA配置文章,加载(编程)速度为毫秒级,所以完全不影响使用。在处理性能上,由于FPGA的逻辑实现是通过硬件编程来获得,所以开发人员可以将指定的算法逻辑,直接以FPGA内部不同门电路的硬逻辑组合来实现,而且现在越来越多的FPGA内部都增加了固化的乘法器、DSP等处理单元,进一步加快了相关运算的处理速度。

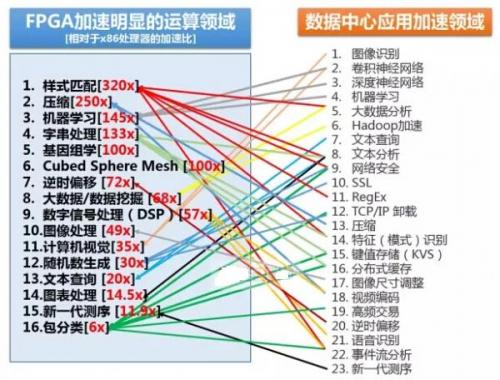

从某种角度上说,FPGA内部其实并没有所谓的"计算",最终结果几乎是"电路直给",因此执行效率就大幅提高。当然,由于采用的是通用的门电路组合,在某些处理效率上FPGA仍然不及ASIC极致,但是可重复更新内部逻辑的灵活性,再加上在固定算法上远高于CPU的执行效率,让FPGA在应用领域迅速得到重视。然而需要指出的是,用FPGA的门电路实现整数运算逻辑,要比实现浮点运算逻辑简单得多,所以FPGA的加速优势也更多的体现在整数性运算,而整数运算正是当前主流企业级应用的主要运算方式,而这也是为什么GPGPU更多的用于浮点运算领域(如HPC),FPGA更多用于整数加速领域的一大原因。

赛灵思总结的,目前FPGA相对于主流的x86处理器,在某些领域里的加速比,以及目前数据中心里可用到FPGA加速的领域,可以说80-90%的大规模并行密集应用都可以被FPGA加速,尤其是以整数型运算为主的应用,加速效果更为明显。当然,并不是说FPGA不能用于浮点运算,但相对来说,整数型加速对于FPGA更容易实现,相较GPGPU也有更明显的优势。另外,请注意很多IT基础设施的底层信息处理方面,如安全、加密、网络加速、键值存储也在FPGA的应用范畴之内,其"实用性"显然比GPGPU更为广泛

但是,传统的FPGA加速设计,均是以I/O总线与CPU平台相连,比如常见的PCIe,在系统内部以一个I/O设备存在,所以在实际的应用中,对于应用开发者本身来说仍然有较大的难度。这次CAPI的出现,则从根本上解决了这个难题,从而让FPGA的加速优势得以获得更充分的发挥。

- 台积电满脸“苹果光”(05-06)

- 智能手机陷入“千机一面”怪圈(06-08)

- CPU/APU:一场无声的反垄断技术较量(06-21)

- 移动设备纷纷采用多核CPU遭质疑:性能过剩(01-12)

- 系统级芯片SoC真的能取代传统CPU?(04-26)

- 国产CPU:放手一搏正当时(05-11)