clock_latency的疑惑

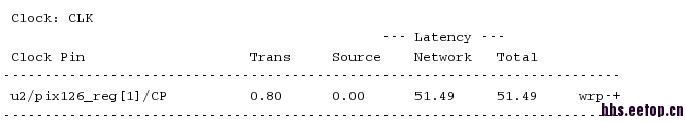

,图片可能有点小了,内容就是:source latency =0network latency=51.49。我的sdc中定义了输入延时:set_input_delay=50。求大神解释下:什么是soure latency 和network latency?输入延时难道是加到network latency上去了吗?求指导!

哪位给这位小弟科普一下?

小编,我看过你之前的帖子,里面有讲这个的,但是source latency 和 network latency哪个包含了输入延时(input delay)呢?时钟树用图形界面检查了也没有什么问题啊,latency一般都在1.3左右,skew=0.2左右。

求科普

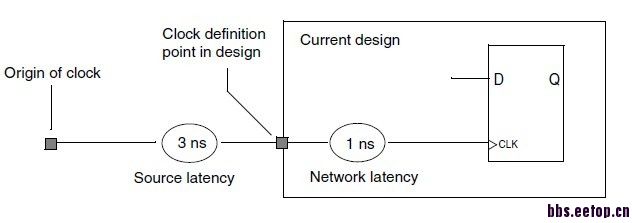

今天又查了点资料,synopsis 的timing guide里有关于latency 的详细说明,先摘抄如下:

Latency is the amount of time it takes for the clock signal to be propagated from the original clock source to the sequential elements in the design, consisting of two components, source latency and network latency.Source latency, also known as insertion delay, is the time it takes for a clock to be propagated from its ideal waveform origin point to the clock definition point in the design.

Network latency is the time it takes for a clock to be propagated from the clock definition point in the design to a register clock pin.如下图所示:

我现在还是有点不太明白,为什么我设置的input delay会加到network latency上去?

看过好多资料。好像发现了点什么东西:

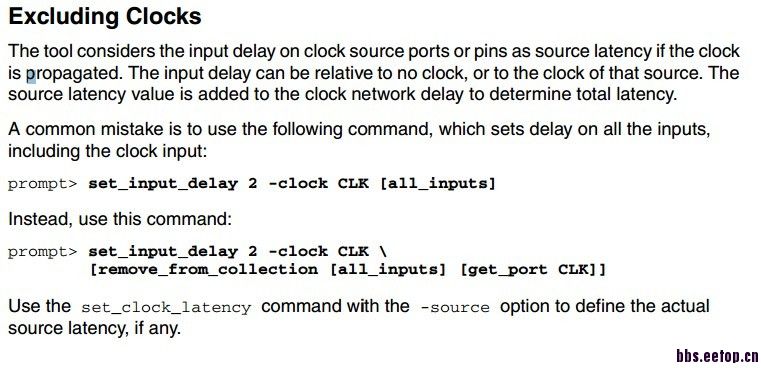

小编,是不是因为我设置inputdelay的时候把所有input都加了,包括了clk,所以tool会默认为我给clock加了一个latency,而这个latency默认情况下是加到networklatency 上的? 我这样理解对不对?

一个人说了这么多,每个人理a

先用report_timing -path_type full_clock_expanded 看看实际的CTS 的latency

如果你怀疑set_input_delay到clock port上了,就把它设为0,再试试呗

改input_delay对report_timing -path_type full_clock_expanded的结果好像没有什么影响。不过将input_delay设置为0后,clock latency 就变成真实的latency 了。若用set_input_delay 2 -clock CLK [remove_from_collection [all_inputs] [get_port CLK]] 这个命令,不会讲input delay加到network latency上去。但是用set_input_delay 2 -clock CLK [all_inputs]后,会将networ latency的值在真实的latency的基础上加2ns

改input_delay对report_timing -path_type full_clock_expanded的结果好像没有什么影响。不过将input_delay设置为0后,clock latency 就变成真实的latency 了。若用set_input_delay 2 -clock CLK [remove_from_collection [all_inputs] [get_port CLK]] 这个命令,不会讲input delay加到network latency上去。但是用set_input_delay 2 -clock CLK [all_inputs]后,会将networ latency的值在真实的latency的基础上加2ns

delay是data上的吧,latency是clock上的吧

很有可能,看来clock-latency加是有范围的

source latency表示时钟从实际的时钟输入端(晶振输出)到模块的时钟port端的延时,network latency表示定义时钟的port端到sink的CP端的延时。没记错的话应该是这样的

嗯 学习了,谢谢!

hao,多谢小编分享,学习了

The set_input_delay command sets input path delays on input ports relative to a clock edge.

学习了

谢谢,学习了

set_input_delay是对input pins设置约束的,是说从外面来的输入信号到达chip的时间,一般时钟周期的50%~70%,是针对input pin的,不是针对clock的。针对clock的是source latency,而network laytency是insertion delay,CTS之后插入了多少delay,欢迎高手指正

在ICC里set_input_delay是会将inputdelay加到clock上去的,如果想要在时钟端不加这个inputdelay,请参考本帖子的七楼。

对啊,七楼的意思是虽然能加在clock上,但是一般没有人会将他加上去,第二个命令不上很清楚吗,把clock pin排除出来了

mark

应该是时钟信号做普通信号,加了input delay,