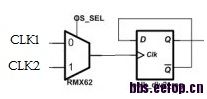

既有MUX后面跟个二分频的DFF,怎样creat clock?

如果CLK1和CLK2没有其他扇出(就是说没有与其他DFF的clock pin连接)的话,在MUX的后面用create_clock生成一个时钟CLK,然后再DFF后面用create_generated_clock生成一个GCLK。

如果CLK1和CLK2还有其他扇出的话,生成2个clock CLK1和CLK2,然后再DFF后使用create_generated_clock -add -master_clock CLK1/CLK2生成2个GCLK,然后设置变量timing_enable_multiple_clocks_per_reg为true就可以了。

多谢指点,那如果用case analysis 应该怎么设置呢?

使用create_clock生成CLK1和CLK2,使用create_generated_clock -master_clock -add 生成2个GCLK。最后用set_case_analysis 0 OS_SEL做分析,分析完了再用set_case_analysis 1 OS_SEL做分析。

我不清楚用set_case_analysis关掉master clock后是否同时关掉它的gclk,你可以试一下,我猜是可以的。

不推荐这种方法,不过最终还是要根据设计本身来决定。

如果按这样处理的话,CLK1和CLK2产生的GCLK之间将会有timing check。我觉得这应该跟design的function不符合。

谢谢!

所以要试一下啊,因为set_case_analysis以后会把CLK1或者CLK2关掉(就是不检查),但是不知道是否会把以它为master_clock的GCLK关掉,所以叫你去做一下实验。如果不能关掉的话就在set_case_analysis 语句后面再create_generated_clock,然后在下一次set_case_analysis时使用remove_clock把那个GCLK去掉然后再重新create_generated_clock。

我喜欢用我在2楼所说的方法,一般我不设置set_case_analysis的,它还会产生还多其他问题的,这个一定要谨慎设置。

赞成2楼的做法,如果5楼的问题出现,set false path

Hi dianyubaobei

我也赞同你在2楼的做法。我只是觉得这种做法还不够完整。

比如,在分频寄存器后生成了gen_clk1和gen_clk2, 分别来自clk1和clk2.

我做了一个小实验,发现gen_clk1和gen_clk2之间有timing check。

是不是应该再加上一些timing exception的setting。

thanks!

嗯。这个是肯定的。我疏忽了。

用 set_clock_groups -logically_exclusive 把两个clock分开。

请教一下 如果clk1 clk2 来自于两个不同的pll, 那么在mux的z端去create clock ,从pll出来到mux输入的timing就没法计算了吧? 用source latency设么? 不过如果clk1 clk2没有别的扇出好像这段路径也没啥影响

学习中...

此贴讨论的太好了非常棒