clock gate cell的结构问题

时间:10-02

整理:3721RD

点击:

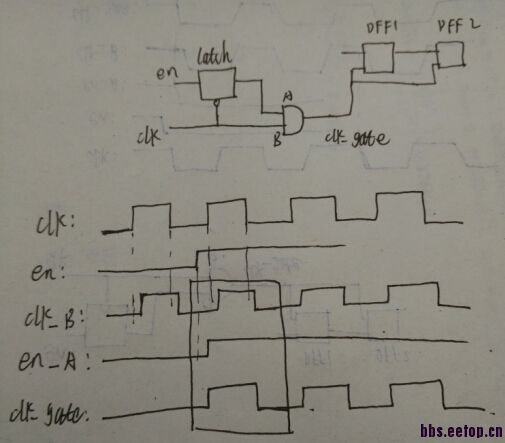

clock gate cell 一般是 low latch+and ; high latch+or呢 为什么不可以是 low latch + or呢

能否结合时序图详细说下呢 多谢了

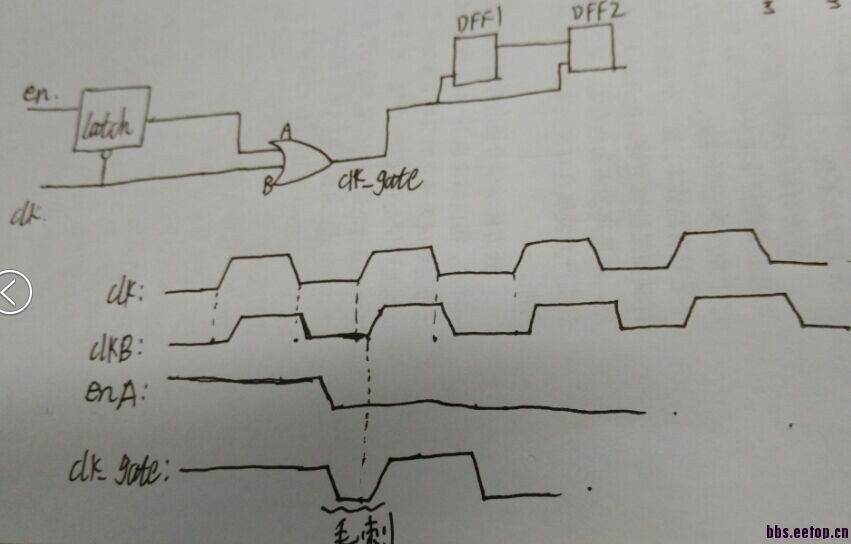

您说的应该是图中所指的毛刺吧

那 一般都是 如下四中情况

为什么不可以使用 rise dff + and结构呢

没看出来有什么问题啊

下面是latch + and 构成的 icg,为什么还是存在毛刺呢? 可以看到 由于 en_A 的关系,可以看到 clk_gate 的第一个脉冲的宽度变大了;

请问这是为何呢?

能否结合时序图详细说下呢 多谢了

你自己首先画一个图,然后分析一下时序,看看 low latch + or,在时钟打开的瞬间,是不是有毛刺出现

您说的应该是图中所指的毛刺吧

那 一般都是 如下四中情况

Low latch+and à

上升沿触发;rise dff+orà

上升沿触发;

High latch+or à

下升沿触发;fall dff+and à

下降沿触发;

为什么不可以使用 rise dff + and结构呢

没看出来有什么问题啊

都有的,分别叫做posedge/negedge icg

版大,我想问下,用 latch+and/or 构成的icg就是为了避免毛刺的

下面是latch + and 构成的 icg,为什么还是存在毛刺呢? 可以看到 由于 en_A 的关系,可以看到 clk_gate 的第一个脉冲的宽度变大了;

请问这是为何呢?

你的gate的enable端来自于哪个clock?为什么会有一个clkb?

en_A 要是来的慢呢?这样不就有毛刺了!

这个gating cell也是有时序要求的,时序满足要求,它的输出就不会有毛刺了!

既然是使能在时钟有效时穿过latch,那么时钟为高之前,latch之后的en就已经稳定了,也就不会出现毛刺了!

clk_B是clk传到与门 B端时的时序

thank for sharing