紧急求助!DC综合后仿真的问题

时间:10-02

整理:3721RD

点击:

对综合后的电路进行了一下仿真,发现出了点问题,截取出问题的代码如下:

always@(posedge clk_rd_i or negedge rst_n_i)

begin

if(!rst_n_i)

empty_buff <= 2'b0;

else

empty_buff <= {empty_buff[0],flag_empty};

end

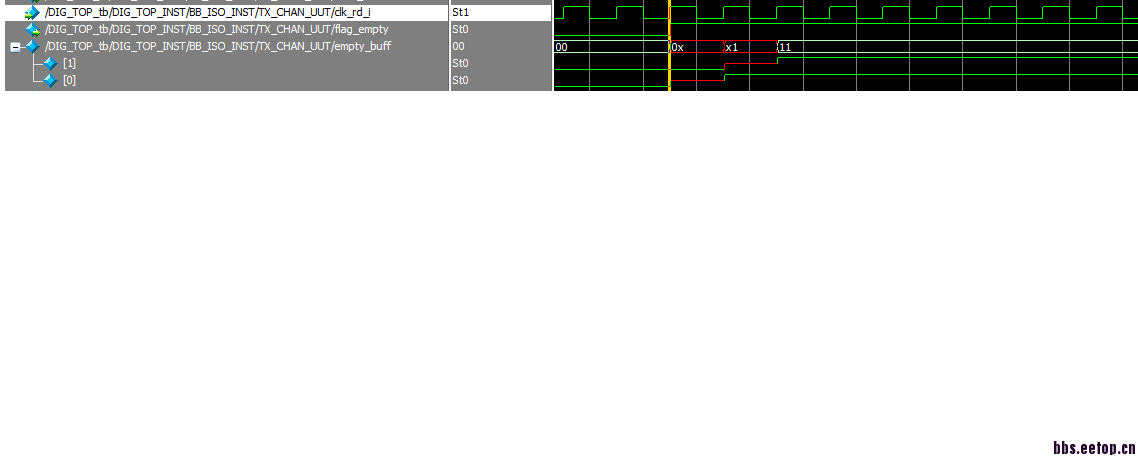

empty_buff[1]用来作为后续部分的控制信号,其实就是对flag_empty进行了两次延迟,截取与这两个变量有关的仿真结果如下图

可以看见,过来的flag_empty信号时没有问题,但是empty_buff信号中出现了x状态,我百思不得其解,为什么会发生这种事情,求牛人指点!

我也出现过这种情况,但是不知道为什么,有没有大牛知道啊?

帮顶一下,坐等高人!

异步处理,仿真器模拟了亚稳态行为。

该代码中flag_empty是在系统源时钟下运算产生的,clk_rd_i是对源时钟进行门控运算后产生的,所以flag_empty对clk_rd_i是异步的,是这样的吧?谢谢你的指点,使我茅塞顿开!

代码里边flag_empty与clk_rd_i确实是异步的,我处理一下试试,谢谢你的指点,我茅塞顿开!

代码里flag_empty是在源时钟下产生的,clk_rd_i是对源时钟在门控信号下运算得到的,所以flag_empty与clk_rd_i是异步的,估计原因就出在这,谢谢你的指点,我茅塞顿开!

这是否意味着题主的写法有问题呢?