local skew 竟然比 global skew 还大?! 百思不得其解啊

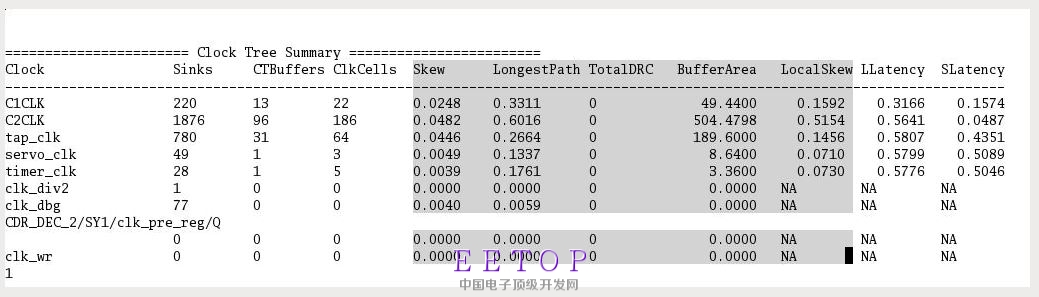

做CTS的时候,发现一个奇怪的问题,report_clock_tree -summary -local_skew 报出来的 local skew 比 global skew 还大,如图:

论坛有个帖子说derate可能导致这种情况,但是我的设计中没有derate;

global skew 是指同一时钟域内,任意两条路径之间的最大skew;

而local skew 是指同一时钟域内,任意有timing path的两条路径之间的最大skew;

理论上说,local skew 应该是小于等于global skew的,为什么这里会出现 local 大于global 的情况呢?

图片怎么不见了? 补发一个

我觉得这个local skew ,会把icg算进去,所以算出来skew会变这么大

正解

可以把option:local_skew改为-local_skew_skip_icg报报看。

谢谢回答!

我重新用 report_clock_tree -summary -local_skew -local_skew_skip_icg 报了一下,结果如下:

分割线下面的部分是 skip icg 情况下的结果,上面是原来的结果。

skip icg 之后,local skew 确实减小了,其中 tap_clk, servo_clk 等几个时钟的local skew 现在小于global skew了,说明确实是考虑了icg导致的;但是C1CLK 和 C2CLK 这两个时钟信号的 local skew 依然大于global skew,是不是这里的local skew 考虑了一些其他的特殊cell 呢?

补充一下,这里的C1CLK 和 C2CLK 都是用create_clock 定义的真实clock,而tap_clk, servo_clk 等都是generated clock(以C2CLK为master clock), 我猜测可能是因为global skew 会穿透这些generated clock 去计算全局的skew,而 ICC 在优化 timing 时默认也会穿透 generated clock 去做优化,所以优化后得到的 global skew 比较小。而 local skew 则不会穿透 generated clock,而是把generated clock 的source pin 当做sink点来计算skew,所以导致 local skew 比较大。 不知道这样理解对不对?

local skew应该是同一个时钟域里面只要有talk的都会去算skew,现在把icg去掉后,还有这么大的local skew,可能是因为divider里面的寄存器没有做平?你去掉-summary报看看呢,看看最小的latency是哪个寄存器

多谢分享!

你的理解是对的,除了icg外,local skew还会报non-stop pin的skew,而non-stop pin在报global skew的时候是穿透过去的,这就造成了两者的差异。

good good good