随路时钟如何平衡时钟

时间:10-02

整理:3721RD

点击:

感谢各位热心帮助我的朋友!

这里还有个问题,就是解决了placment 之后,CTS也过了。但是有随路时钟的问题导致timing很难met。所以想请问

各位大侠,用何种方式才能将随路时钟搞定啊?

这里还有个问题,就是解决了placment 之后,CTS也过了。但是有随路时钟的问题导致timing很难met。所以想请问

各位大侠,用何种方式才能将随路时钟搞定啊?

具体的时钟结构如何?整个图看看?

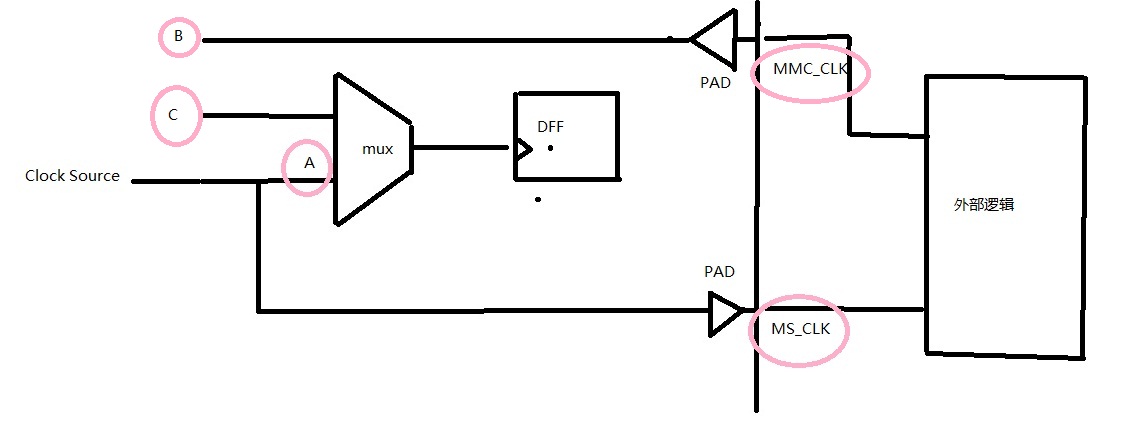

大致画了一个示意图 ,请大侠指教!

也和同事讨论了一下,他的要求是要从clock source 端 到A点和MC_CLK PAD 的delay是相同的,这样timing就应该可以了。

这个图可能有点不清楚,B点和C点的连接关系等弄清楚了再补充。

所以我就想知道如何平衡A 点和MC_CLK PAD之间的clock delay。

设置为stop pin,单独做balance,不可以吗?

這些都看不太懂

这个搞定了。多谢大侠们关注!

估算充clock source 到PAD MS_CLK 的delay ,让后再做clock tree的时候,将clock source delay设置成

上面计算的delay值。这样综合出来的clock tree就可以满足时序的要求了。

同一楼上,cool

Group到一起,Tools就回去Balance这2个Clock之间的Skew了。

学习。

先试试看~紫薯布丁