求教关于DFT的preview_dft的错误问题

Warning: Design 'design_top' contains 1 high-fanout nets. A fanout number of 1000 will be used for delay calculations involving these nets. (TIM-134)

Information: Starting test design rule checking. (TEST-222)

Error: Invalid test protocol. Create a test protocol again. (TEST-1310)

Error: Could not run pre-dft design rule checking. (TEST-1313)

Information: Defining new variable 'hlo_collapse_intermediate_hardware_alts'. (CMD-041)

0

2、下面是我对设计的configuration,是在DC综合完后,做以下设置的

set hdlin_enable_rtldrc_info true

remove_attribute[get_designs -hierarchical{*}] dont_touch

set test_default_scan_stylemultiplexed_flip_flop

set_scan_configuration -stylemultiplexed_flip_flop-clock_mixing mix_clocks -add_lockup true -chain_count 1

set_scan_configuration-lockup_type latch

set_dft_signal -view spec -type ScanEnable-port SCAN_EN -active_state 1

set_dft_signal -view existing_dft -type Reset -port RESET-active_state 0

set_dft_signal -view existing_dft -type ScanClock-port XTAL1 -timing {45 55}

set_dft_signal -view spec -typeTestMode -portTEST_MODE-active_state1

set_dft_signal -view spec -type ScanDataIn-port SCE_P

set_dft_signal -view spec-type ScanDataOut -port SIO_P

set_scan_path -view spec c0 -scan_data_in SCE_P -scan_data_out SIO_P

set test_default_delay0

set test_default_bidir_delay0

set test_default_strobe40

set test_default_period100.0

set test_default_strobe_delay1.0

compile -scan

preview_dft

3、由于是第一次做DFT,所以有很多疑问,也有很多理解不到位的,希望各位大神指教,嘿嘿,谢谢大家啦!

首先,上面所说的 Invalid test protocol.是不是就是指我的scandft和testconfiguration的所有设置。

其次,set_dft_signal -view spec -type ScanEnable-port SCAN_EN -active_state 1命令里面的view设置会不会影响扫描链的生成,我将原来预留给测试用的端口设置为existing的,复用其他IO端口的设置为spec,不过提示时钟也要设置为spec。我们复用其他IO端口的时候,对端口有什么特殊的要求吗?

还有里面的active_state我们是根据什么进行设定的呢?

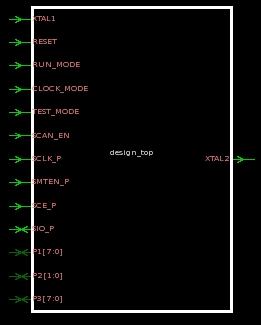

下面是我的模块的顶层端口

加上 create_test_protocol

好的,谢谢!为什么结果出来,我里面没有扫描链

****************************************

Preview_dft report

For: 'Insert_dft' command

Design : design_top

Version: B-2008.09

Date: Tue Mar 11 04:14:57 2014

****************************************

Number of chains: 0

Scan methodology: full_scan

Scan style: multiplexed_flip_flop

Clock domain: mix_clocks

Scan enable: SCAN_EN (no hookup pin)

No chains

************ Test Point Plan Report ************

Total number of test points: 0

Number of Autofix test points: 0

Number of Wrapper test points: 0

Number of test modes: 0

Number of test point enables : 0

Number of data sources: 0

Number of data sinks: 0

**************************************************

Dft signals:

TestMode: TEST_MODE (no hookup pin)

1

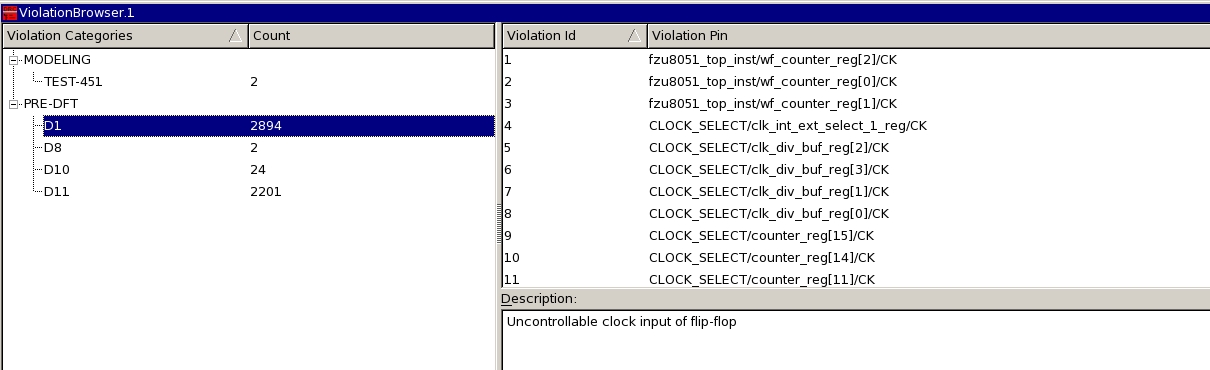

而且dft_drc出来有很多错误:

加上 autofix

看 <<TetraMAX on-line help>>

好的,谢谢!

我将TEST_MODE 和XTAL1设置为TestData ,然后set_autofix_configuration 设置失败,请问一下,这边的控制信号,应该是由测试的控制信号控制的?

set_dft_signal-view existing_dft -type TestData-portTEST_MODE

set_dft_signal -view spec -type TestData-portXTAL1

design_vision> set_autofix_configuration -type clock -control_signal TEST_MODE -test_dataXTAL1

Discarded Autofix configuration specifications.

0

TEST_MODE 不要设成 TestData, autofix 是用它去 control 其他 signal

RESET 需要 autofix, 用上 -active

很谢谢您的回答!

现在set_autofix_configuration 设置成功,就是不知道TEST_MODE为什么一定要设置成spec才行,现在preview_dft的结果也是正确的。

但是dft_drc的出现的错误貌似没有自动修复,是不是因为我里面的宏模块没有做特殊的处理:

1、出现在flash和osc上面的错误

(fzu8051_top_inst/FLASH_32KB (Cell fzu8051_top_inst/FLASH_32KB (PF32K09E) is unknown (black box) because functionality for output pin VDD is bad or incomplete.) )

2、出现在clk和reset上面的四类错误

D1:Uncontrollable clock input of flip-flop

D8:Clock not able to capture

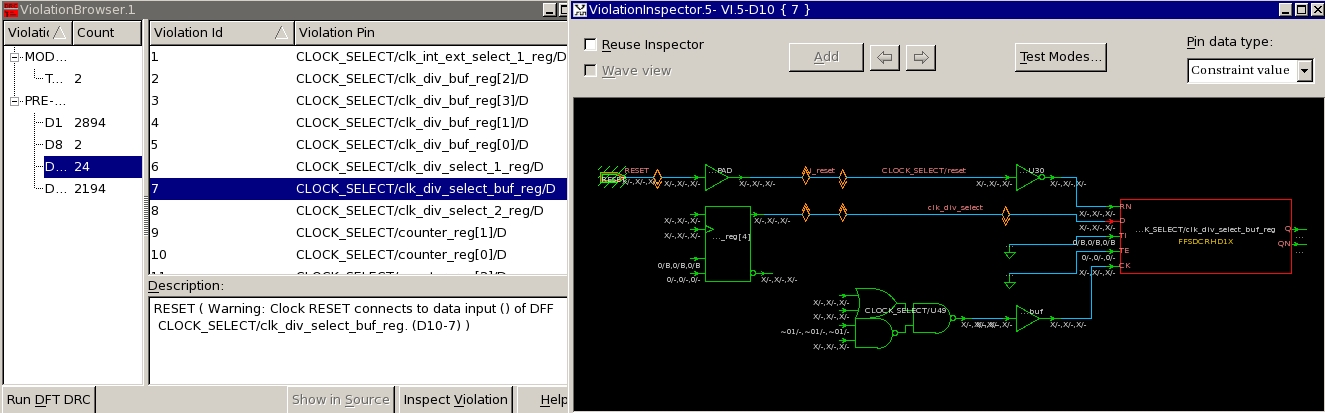

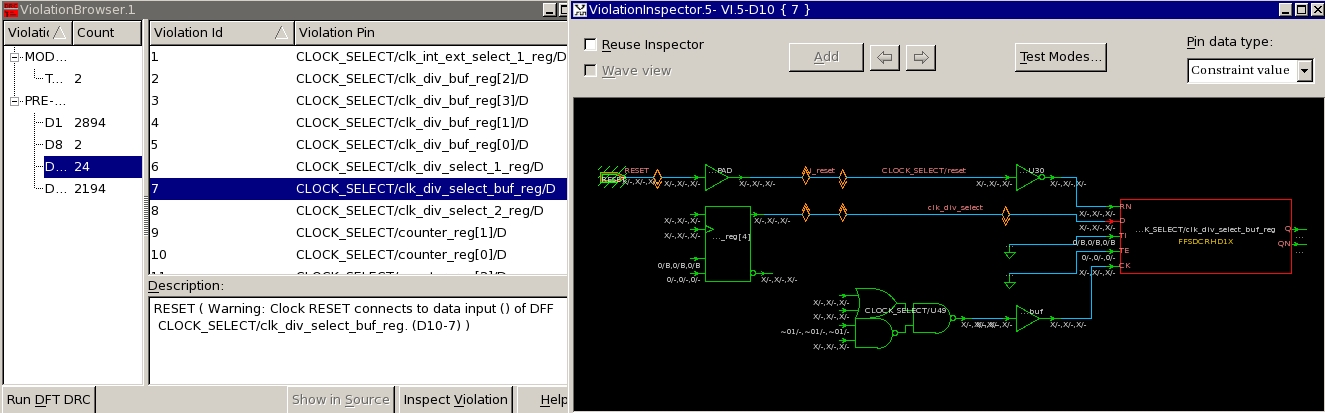

D10:Clock feeding data input

D11:Clock feeding both clock and data input

下面是报错寄存器上面时钟端口出现的错误:

谢谢您的回答!刚才发的帖子给没了。

按照您的提示,已经设置成功,不过TEST_MODE的view一定要为spec,才能设置,不知道什么原理,现在preview_dft的结果也正确。

就是drc_dft依然出现错误就是了,clk和reset上面,不知道是不是我又两个宏模块flash和osc没有进行处理的缘故。

1、宏模块所报的错误:RING_OSC_24M (Cell RING_OSC_24M (ringosc_rc) is unknown (black box) because functionality for output pin VDD is bad or incomplete.)

2、clk和reset出现了好几类的错误。

我是这样理解的,在此之前这些 port 没有用在 DFT mode, 就用 spec, 如果在 DFT mode 已经使用的话,就用 exist

关于 hard macro 的话可以修改 RTL 去 bypass. 使用 command 的办法我没有找到,如果你有找到并尝试成功的话请告知我。

set_dft_configuration -fix_*

其实 google 上能搜到很多资料,而百度却是很缺乏的

恩恩,好的,谢谢您!嘿嘿

我把自动修复都使能还是不行,我去试试吧宏模块处理一下,看行不行。

Thanks....