DFT设计的问题

各位谁能告诉我这个问题怎么解决么?在没有加入低功耗设计之前么有问题,加入低功耗设计就出问题了,搞了很久都没有解决。很是纠结!

Error: Chain chain0 blocked at DFF gate watchdog/wdt_ctl_reg_reg[7] after tracing 2265 cells. (S1-1)

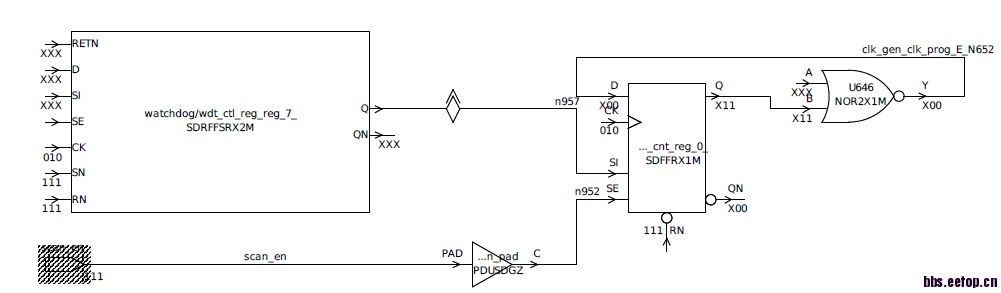

附图:

编写的脚本如下:

set test_default_delay 0

set test_default_bidir_delay 0

set test_default_strobe 30

set test_default_period 100

set_scan_configuration -chain_count 1 \

-style multiplexed_flip_flop \

-clock_mixing mix_clocks \

-internal_clocks none \

-add_lockup true \

-reuse_mv_cells false \

-power_domain_mixing true \

-mix_internal_clock_driver true

set_dft_insertion_configuration \

-synthesis_optimization none \

-preserve_design_name true \

-route_scan_enable true \

-route_scan_serial true

set_dft_configuration -scan enable \

-fix_xpropagation enable \

-fix_clock enable \

-fix_reset enable \

-fix_set enable

set_dft_drc_configuration -clock_gating_init_cycles 1

set_dft_signal -view existing_dft -type ScanMasterClock \

-port clk -timing [list 45 55] \

-hookup_pin [get_pins clk_pad/C]

set_dft_signal -view existing_dft -type ScanSlaveClock \

-port exclk_rtc -timing [list 45 55] \

-hookup_pin [get_pins exclk_rtc_pad/C]

set_dft_signal -view existing_dft -type Reset \

-port rst_in_n -active_state 0 \

-hookup_pin [get_pins rst_in_n_pad/C]

set_dft_signal -view spec -type ScanEnable -port scan_en -active_state 1

set_dft_signal -view spec -type TestMode -port scan_mode -active_state 1

#chain0

set_dft_signal -view spec -port misoi -type ScanDataIn \

-hookup_pin [get_pins misoi_pad/C] \

-hookup_sense non_inverted

set_dft_signal -view spec -port mosio -type ScanDataOut \

-hookup_pin [get_pins mosio_pad/I] \

-hookup_sense non_inverted

set_scan_path chain0 -view spec -scan_data_in misoi -scan_data_out mosio

set_dft_signal -view spec -type TestData -port clk -hookup_pin [get_pins clk_pad/C]

set_dft_signal -view spec -type TestData -port rst_in_n -hookup_pin [get_pins rst_in_n_pad/C]

set_dft_signal -view spec -type TestMode -port scan_mode -hookup_pin [get_pins scan_mode_pad/C]

set_autofix_configuration -type clock -control_signal scan_mode -test_data clk

set_autofix_configuration -type set -control_signal scan_mode -test_data rst_in_n

set_autofix_configuration -type reset -control_signal scan_mode -test_data rst_in_n

create_test_protocol -capture_procedure multi_clock

DFT 是离散傅里叶变换吗

不是,是design for test的意思!

连个图都没有,谁知道怎么解决。

在Tmax中打开GUI, 分析一下S1 violation.

SE 端应该是111, 现在是XXX,你顺着往前找吧。

SE端是111,是scan_en,DFT设计的使能端,图上就有!

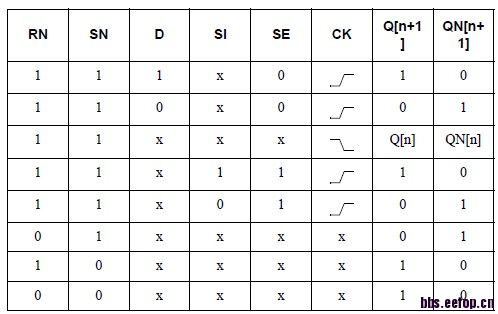

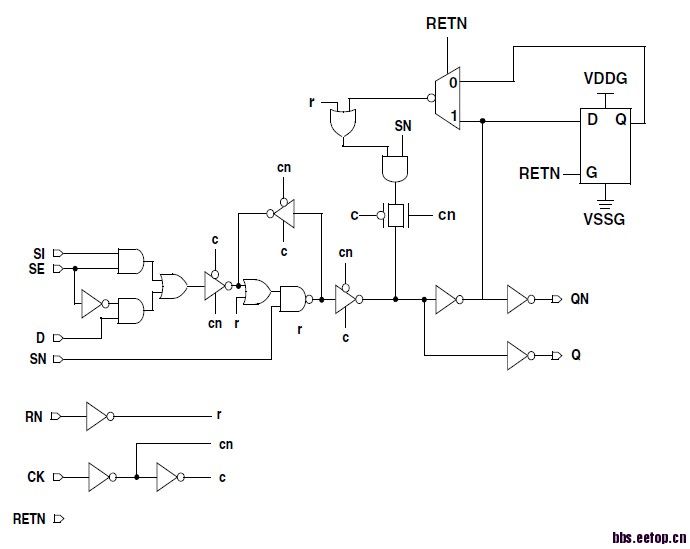

RETN是个什么pin?RN和SN都是低有效?

reg_reg_7 这个寄存器的SE端图上没看出来111,如果你确认是111 那就ok。

还有就是楼上说的RETN是什么功能信号呢,XXX是否影响寄存器的Scan功能。

Cell Description

The SDFFSR cell is a positive edge-triggered, static D-type flip-flop with scan input (SI),active-high scan enable (SE), and asynchronous active-low reset (RN) and set (SN). Set (SN) dominates reset (RN).

again,what is the function of RETN?

o,I'm sorry.搞错了,你说的那个信号是低功耗信号,保持使能端

那你RETN是X怎么可能对呢?

嗯,我试试看

经检验,发现我的设计有些纰漏,低功耗设计跟所用的工艺库相关,导致了一些纠结的问题。

您好,想请问一下

1、您命令set_dft_signal -view existing_dft -type Reset-port rst_in_n -active_state 0 里面的

-active_state是怎么确定的呢?

2、如果我的顶层端口只有SE和test_mode的话,我其他端口是不是要复用其他的输入输出,如果可以,是不是只要是输入输出出端口我就可以拿来复用?

3、一般要根据什么确定需要加入多少条扫描链呢?

4、-view existing_dft /spec我看了下文档这样理解对吗:existing_dft是顶层端口本来就设计为扫描输入的,而spec的端口,则是复用的其他IO端口,用于DFT的时候,工具还得添加单元。

谢谢!

good info. thank you.

看看小编的问题怎么解决的

1、reset的01设置要根据你的rtl,如果异步复位低有效设0,反之设1;

2、scan IO设置要根据芯片封装,不是所有的管脚都能复用,比如不封出来的;

3、扫描链的条数越多越好,这样链长会短些,节省测试时间;

4、-view existing_dft /spec: exist表示逻辑电路已经存在,只是单纯地定义下方便工具识别;spec表示逻辑电路不存在,要求工具在插入DFT时需要额外增加电路来完善功能的;

学习一下。

没怎么看懂哈哈。

Back track and find the issue.....