DPLL 设计

请问这样的dpll如何实现,谢谢啦!

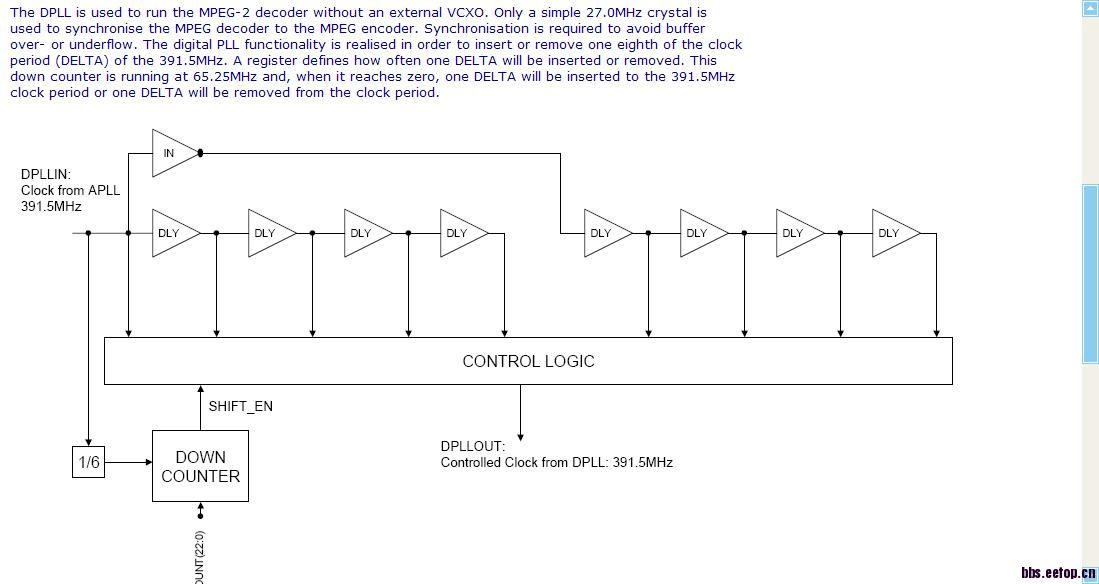

The DPLL is used to run the MPEG-2 decoder without an external VCXO. Only a simple 27.0MHz crystal is

used to synchronise the MPEG decoder to the MPEG encoder. Synchronisation is required to avoid buffer

over- or underflow. The digital PLL functionality is realised in order to insert or remove one eighth of the clock

period (DELTA) of the 391.5MHz. A register defines how often one DELTA will be inserted or removed. This

down counter is running at 65.25MHz and, when it reaches zero, one DELTA will be inserted to the 391.5MHz

clock period or one DELTA will be removed from the clock period.

图画得挺清楚了嘛,DLY单元加上控制逻辑就实现了呗。

没做过....学习学习

请问小编,

如何保证DELTA为1/8个391.5mhz的时钟周期呢?

我不是后端版的小编啦,我是来凑热闹学习的啦。

我仔细看了看这个图,下面谈谈我的理解吧,你看看有米有用:

首先假设反向器的延迟与DLY延迟相比较小。

1-8个DLY是组成了两条链,左四个一条,右四个一条,两条链的对应点呈反向关系。

这样呈反向关系的两条链就能靠输入的0r(0r表示在0个DLY延迟处的rise)事件转换成{0r,1r,1f,2r,2f,3r,3f,4r,4f}这个事件集合

通过挑选集合中的事件搭建满足各种目标频率的波形

2-如果control logic是静态配置的话,输出DPLLOUT端频率固定,最高可以出一个周期=2*DLY的时钟波形(此时DLY值和DPLLIN的频率需要匹配)

3-看起来还有个down counter,会引入动态配置的可能,图里面还说数到0时要插入一级(使DPLLOUT频率变化?),我没有看过MPEG-2协议,它是需要一个时变的DPLLOUT时钟吗?

4-设计DLY时要使它们的延迟尽量相同,等于变化的梯度值,设计时要考虑工艺漂移,ocv等。

以上就是看到电路的一些直观感觉了,抛砖引玉~

没做过....学习学习

在MPEG-2中,decoder时,本地时钟与encoder时钟可能有差异,为了使解码时钟与encoder时钟保持同步,常常通过PCR时钟与本地时钟之差,来补偿本地时钟,达到跟踪encoder时钟的效果。

另外,如果不用DPLL的话,还有其他方法吗?上面的图例来自于一款芯片的datasheet。

请知道的大牛们说说,谢谢!

learning !

学习学习学习