有人碰到过Calibre LVS通过但流片出来VDD和VSS短路的情况吗?

最近在T65 下碰到这种情况,5个人花了3天时间反复检查gds数据,重新做LVS、ERC,还是没发现哪里短路了。

真是点背啊,5年前在S 0.18um工艺下流片就碰到过类似情况,找了一个多月没有找到短路原因,后来S给优惠重投了一次,就好了。

恳请高人指点迷津,可以从哪些方面着手查找原因呢?

erc有没有 soft connect,或者其他error, soft connect通过od,nwell,psub连接也算吧,

怎么查出short的, 是没法上电是吧 ,泄漏电流很大?

顶起,求高人指点!

还没有上电,用万用表测量VDD和VSS凸点之间的电阻只有0.2ohm左右,用万用表的二极管特性档位测量VDD和VSS凸点之间的电压只有20多mV,板级工程师和封装厂的工程师都说是短路了!

btw:同一个圆片上的另一个设计芯片的VDD和VSS之间电阻有4ohm,上电后可正常工作。

难道是封装和 pcb级别的error?

先是在封装后的芯片上直接用万用表测试发现VDD和VSS之间阻值很小(0.2ohm),后来请封装工程师在划片后封装前的裸片上用万用表测试二极管特性,VDD和VSS凸点之间电压只有20多mV。应该可以排除PCB和封装管壳的问题。

补充下ERC检查的结果,ERC报告下列问题:

1、mnpg(MOS erc_nmos_gates S/D connect to POWER&GROUND)

2、mppg(MOS erc_pmos_gates S/D connect to POWER&GROUND)

3、npvss49(ntap connect to GROUND)

4、npvdd49(ptap connect to POWER)

5、floating.nxwell_float(nxwell_float is not connected to POWER)

6、floating.psub(psub is not connected to GROUND)

其中,1、2、3、4发生在TSMC standIO PVSS1ANA/PVSS1DGZ等单元内,TSMC IO手册明确说明需要waived;

5发生在编译产生的memory内部,6发生在模拟PLL内,应不会导致VDD、VSS短路。

还真没碰到这种情况,

设计中有没有block box的IP,merge后有没有做过LVS?

另外foundry生产时也可能有问题,他们应该有一些测试的数据,看看有没有异常。

我碰到过foundry为了省成本,把光刻胶的厚度减小了,NW注入时,很多地方挡不住,直接穿过去了,结果良率一塌糊涂……

有过几年经验的老鸟想LVS把VDD/VSS弄短接的概率很小很小的

不排除foundry的ESD没做好,或其他原因

可以要照片看看

memory 怎么会floating nwell呢,

pll 的floating psub怎么回事,

可以看看,nwell,pwell没有偏置会造成latch-up,不知道是不是这个原因

我们走的是private MPW,一起流了两个芯片,同一批原片上的另一个芯片测试功能正确,频率达到要求,所以目前很难说foundry把什么层做错了。

发现短路的这个芯片没有需要merge gds的IP,而另一个功能正常的芯片反而是做了IP merge的。

芯片还没有加电,会受ESD和latch-up问题的影响吗?

ERC一般在IO和analog IP中都会报一些,确认没问题的话就行

ESD一般会击穿栅氧,不会造成VDD-VSS短路吧

latchup应该是加电时才会发生,可能会烧掉芯片,不过不会裸片就短路吧

对于LVS,检查一下rule有没有问题

foundry的PCM/WAT结果可以要过来看看,虽然另外一个芯片没问题,

有没有一些特殊器件,电阻电容之类的,测试ok的芯片里面没用过

谢谢各位的指点,今天联系foundry了,暂时没有回音。

我们当初向foundry提交gds数据时,两个芯片是单独的gds,foundry在做mask时是怎么一个过程,有没有可能只把其中一个芯片的某些层弄错,而另外一个芯片又是对的?

另外,请教一下,foundry方面有哪些方法可以检查这类问题?

同批次的其他流片的公司,可以打探一下,呵呵

同批次的芯片都是我们的,private mpw,呵呵

报告进展:

1、与foundry工程师讨论后,仍然没有发现流片数据及工艺生产问题,在这要赞一下T的工程师,很认真负责的跟我们开电话会议讨论问题可能的原因;

2、怀疑封装厂工程师用万用表测量圆片的方法不对,昨天让自己的工程师出差到封装厂在测试台上用探针对圆片进行测量,发现core VDD加到1V时电流约70mA,应该没有短路;

3、重新测量封装管壳,没有短路,但核对每个bump的时候,发现管壳设计方将一列VDD VSS bump与另一列信号bump弄反了,造成封装后VDD和VSS短路,现已让他们重做管壳;

这么一个简单问题,折腾我们十多天了,现在终于可以松口气,同时也对国内的某些封装和管壳设计公司很是失望啊!

赞小编的职业精神!

给大家更好的实例参考经验!

本小编奖励200信元!

HELP:请教小编或小编:::::发现短路的这个芯片没有需要merge gds的IP,而另一个功能正常的芯片反而是做了IP merge的。:::

其中的IP merge是什么意思?给我eg解释下。

谢小编发过年红包啊,

购买、使用IP设计公司的IP硬核时,如果只购买了使用权,是拿不到该IP的gds数据的;流片时需要双方将各自的gds都提交到foundry那里,然后将该IP的gds合并到芯片gds中,从而产生完整的流片gds,这个过程叫IP merge。

THX 小编的热心和耐心的帮助。希望群里的大牛们都像小编这样多多share这些实践经验。大赞小编一个know this wafer lot can be accepted or not.

请教一下,

芯片的latch up效应是啥意思,怎么发生的啊?

谢谢啦~

先恭喜小编顺利解决问题

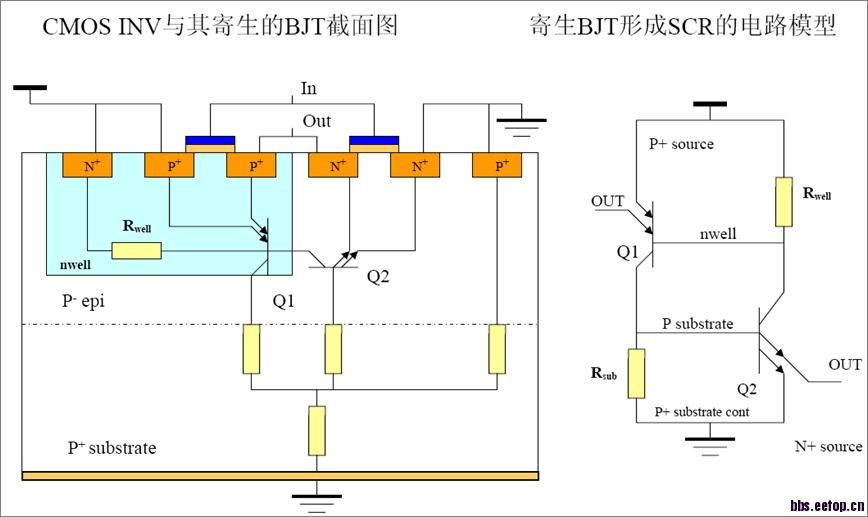

latch up,即闩锁效应,COMS中存在PNPN结构,其中寄生的BJT在一些条件下可以形成正反馈,以至于VDD-VSS之间电流越来越大,不及时关电源情况下,会造成芯片烧毁。

看看下面这个图,版图中一般做好电源和地的衬底接触,减小Rsub和Rwell来防止latch up发生。

感谢小编,这是一个具体的分析、排除、解决问题的过程。

原来是封装造成的,我倒啊,

看来wafer test 还是很有用的,

一般CP 放在FT 之前,就是为了测试wafer上对否,

如果FT 有问题,而cp 没问题,那肯定是封装的问题了

还是foundry出了问题!

谢谢LZ的善始善终,跟大家分享经验。学习了。

感谢小编的分享

问题描述,状况分析,详细的结果,

赞

学习了!如此完整的过程。

作为菜鸟还没遇到过各种奇异的事情。