set_disable_timing 与 set_false_path 差别

set_false_path只对数据路径有效。

差不多,只是写法差别

set_disable_timing 工具完全不去分析; set_false_path 工具还会分析,只是不报出来violation

set_false_path,tool还是会继续优化DRV的。

顶。我觉得最大区别就这个,特别是PT里。

disable 是对arc 起作用的, false_path是对timing path

arc 的disable对path也是有影响的

set_disable_timing require less computation and memory thanset_false_path

set_false_path和set_disable_timing区别:

1. set_false_path有选择性地disables the arrival time information depending

on优先的rules;

2. set_false_path不影响constant values;

3. set_disable_timing物理上剪掉一个timing arc,所以arrival times和constant values都不能穿过arc;

4. all cases可以应用set_disable_timing到valid timing arcs。

谢谢指导!

大家的分析让人受益匪浅。感觉set_disable_timing还是要慎用为好,是吗?

顶 small chip

set_false_path是告诉STA工具,这条timing arc仍然存在,但是不用进行时序分析。

set_disable_timing 是告诉STA工具,这条timing arc在设计中不存在即使 单元库中包含这条timing arc

学习了

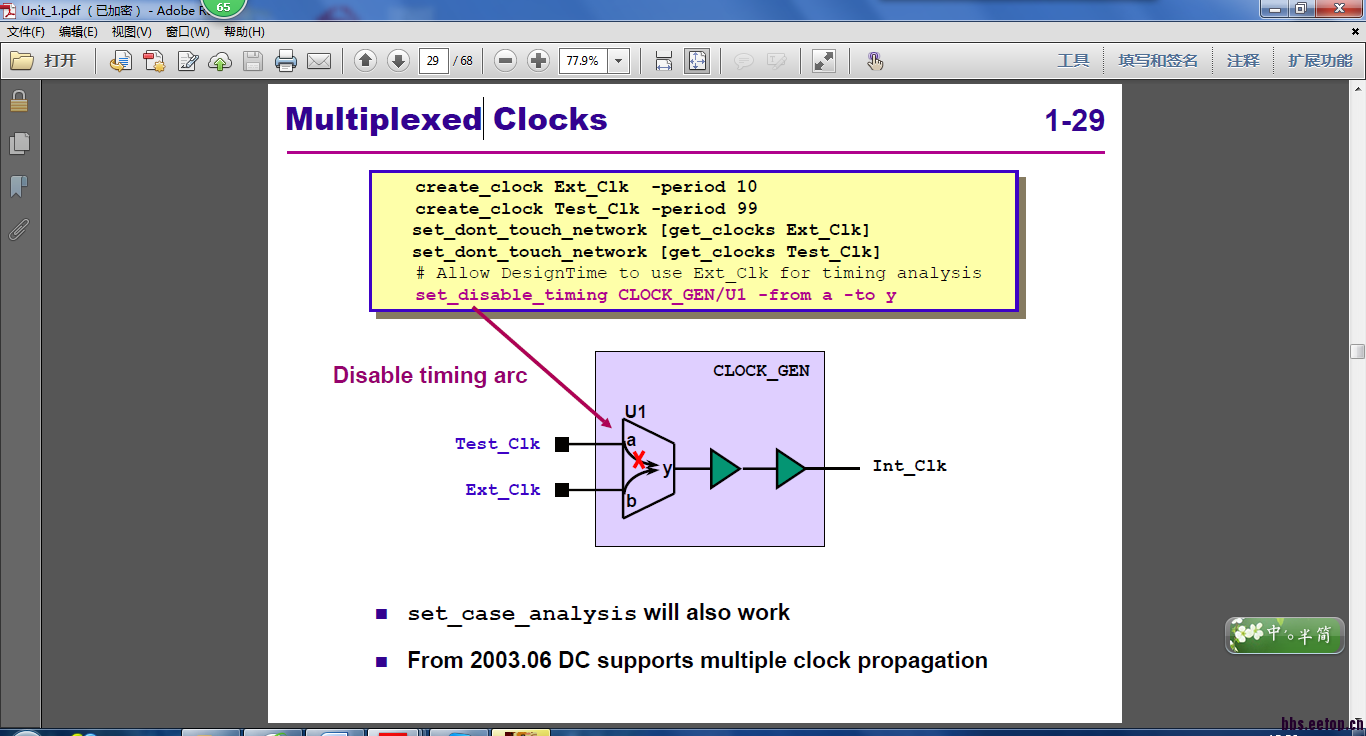

想问一下,两篇PDF中报告的有点出入,你看下:第一篇中有一段话:

One should use caution when using the set_disable_timing command as it removes all timing paths through the specified pins.

第二篇中:

那按第一篇中所说,是不是所有经过 a和y的路径都不会进行分析,但是第二篇中说 还会对 Ext_Clk到y这条path进行分析,这是不是矛盾了呢

a到y的arc被打断了,所以不去分析了,可是b到y还是存在的,所以还是分析,不知道这样对吗?

受益匪浅,谢谢