DC和PT时序分析不一样

由于课程作业要求,小弟最近在跑IC设计的流程,在做到DC和PT阶段的时候,遇到了一些问题。

1.首先,关于DC之后是否要使用PT的问题。小弟也看了不少的资料,很多资料写到DC之后是要做PT的,这个称之为pre_layout STA。但是我又在eetop上看到好多人说DC之后没有必要做PT。所以,我想问的是,到底要不要?

2.我假设DC之后需要做PT,就像很多教程上面说的一样,具体步骤如下:

一.读入DC综合之后的网表文件(.v),并设置current_design

二.读入DC综合之后的时序约束文件.sdc

三.report_timing得到想要的时序信息

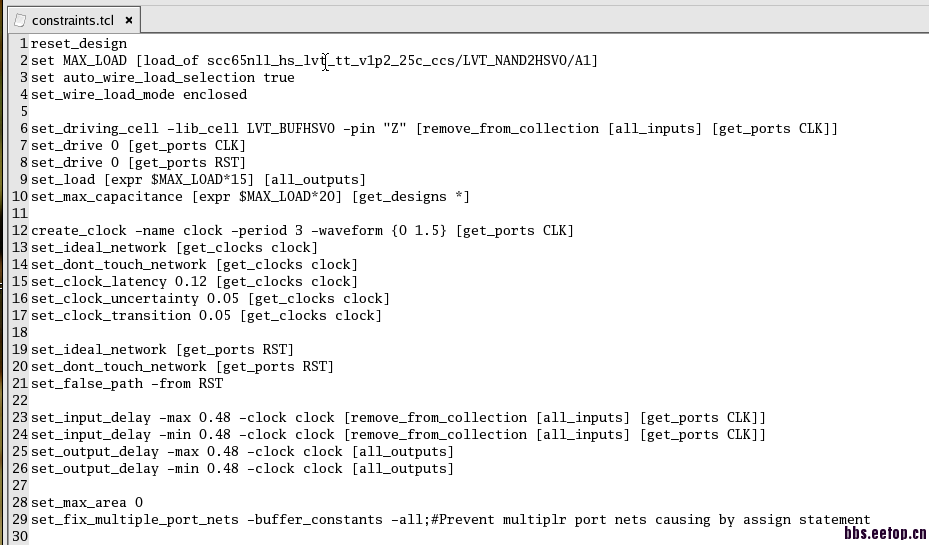

那么,按道理说,时序约束一样的话,在pre_layout阶段两者的时序报告文件应该没有太大的差异。但是我按照上面的步骤跑完PT之后,得到的时序文件和DC的差异很大,具体如下:

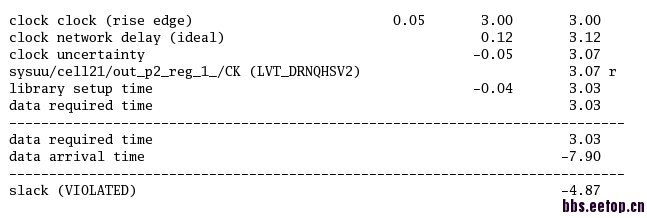

时序约束文件为:

在.synopsys_dc.setup和.synopsys_pt.setup中关于

search_pathtarget_library link_library symbol_library 等都是设置一样的

然后两者得出的报告文件如下:

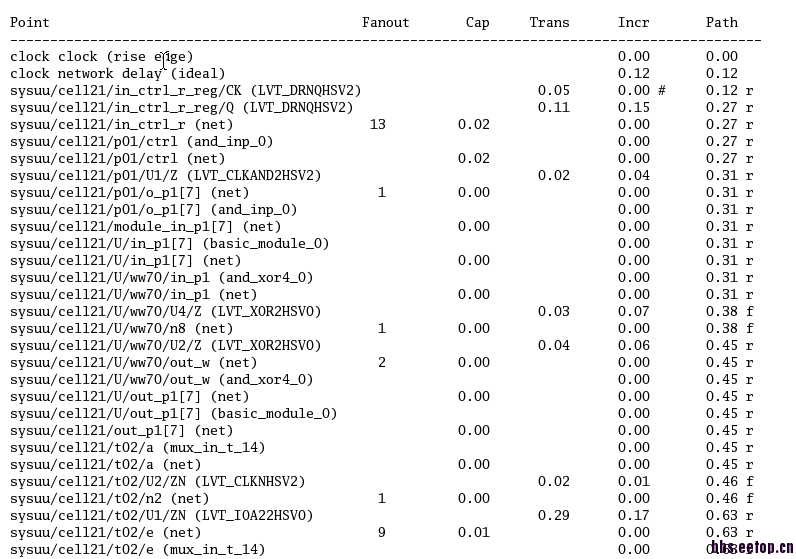

DC中报告如下(路径较长,只显示部分),data arrive time 为2.50 data required time为3.04

显示setup时间是没有违背的

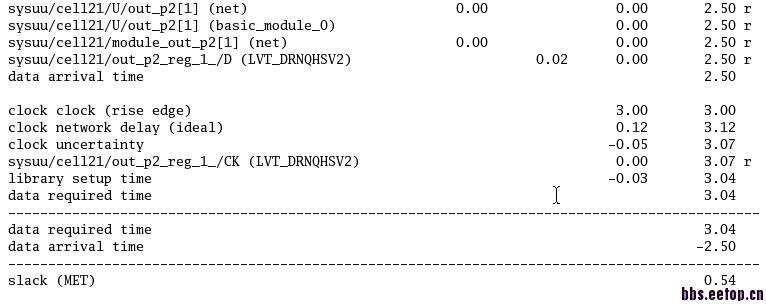

PT报告如下(路径较长,只显示部分),data arrive time 为7.90 data required time为3.03

显示setup时间是有违背的,而且还特别的大

虽然两者的路径是不一样的,但是也不至于差别这么大吧?不过仔细观察报告文件可以看出是因为capacitance和transition_time不一样引起的,PT中的这这两个值比DC中的大得多,不知道这个是什么原因啊?两者设置的工艺库文件都是一样的啊?百思不得其解,望大神帮忙!

辉哥?

DC和PT报出来的明显不是同一条path 没有任何比较性 有vio的地方是faout过大造成的 由于这个米有layout,那只要把fanout的问题解决 就可以修掉的第一个问题 站在后端的角度看 这个pre layoutPT是完全没有必要做的

请教小编个问题,本人是刚学习DC,怎么把报告窗口化您知道吗?在原先公司中source tools/procs.tcl文件就行,但是现在换个工作环境,为何不行了呢。v report_timing 任何提示没有,求解啊。

你把arrival time为7.9ns的路径再截来看看,图片被论坛log挡住了。我加了一下也没有发现你的arrival time有7.9ns啊

完全没有必要做?那一般什么时候需要用到PT呢,我也是初学者,希望大神多多赐教!

可能是工具算法不同使dc和pt结果不同

PT是专业STA signoff的工具,使用的算法肯定更精确,而DC,ICC用的算法不够精确,会出现在DC 、ICC报告出的时序不同

一般来说做了会好点,反正也不是很麻烦

毕竟post layout还是要用pt来看timing,pre layout先用pt过一次

假如有问题也好做比较

顶贴赚积分