ICC抽取sdf文件后用NC-verilog仿真,有很多timing violation

时间:10-02

整理:3721RD

点击:

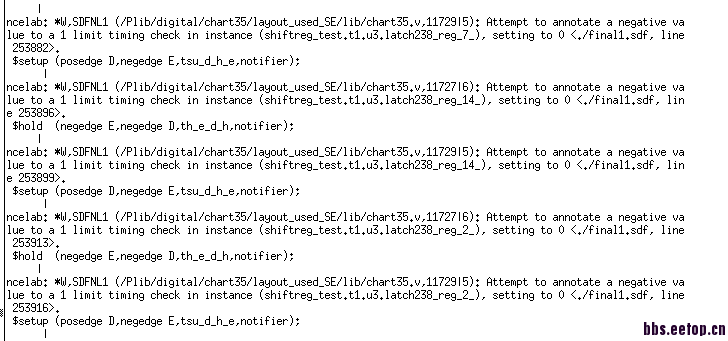

今天用ICC做完APR之后,用write_sdf 命令导出了sdf文件。因为刚入门不久,所以不太会用STA和形式验证的工具,就用APR后抽出的网表和sdf文件来做仿真。用的是cadence的NC-verilog。但是发现仿真时会报很多警告:

我用ICC导出sdf文件的命令是write_sdf ./final1.sdf

在ICC里面仔细查过了,没有timing violation。求教大神有没有知道可能是什么原因啊?求指导!

我怀疑是ncverilog将负值变成0 了,导致时序变差了。ICC里的timing slack都是大于0的,没有violation

我用ICC导出sdf文件的命令是write_sdf ./final1.sdf

在ICC里面仔细查过了,没有timing violation。求教大神有没有知道可能是什么原因啊?求指导!

真心求教! 在线等!

检查仿真的时序与ICC的sdc是否一致

陈小编,我看过了icc的sdc了,和仿真的时序是一样的。在ncverilog编译的时候会报以下警告:

我怀疑是ncverilog将负值变成0 了,导致时序变差了。ICC里的timing slack都是大于0的,没有violation

那也有可能

请问小编,怎样让ncverilog对负值也能标注?我用了+neg_tchk以后,没有作用啊

(CELL(CELLTYPE "lanhq1")

(INSTANCE u3/latch13_reg_12_)

(DELAY

(ABSOLUTE

(IOPATH (posedge E) Q (0.377:0.377:0.377) (0.333:0.333:0.333))

(IOPATH D Q (0.243:0.243:0.243) (0.252:0.252:0.252))

)

)

(TIMINGCHECK

(WIDTH (posedge E) (0.200:0.200:0.200))

(SETUP (posedge D) (negedge E) (-0.016:-0.016:-0.016))

(SETUP (negedge D) (negedge E) (0.076:0.076:0.076))

(HOLD (posedge D) (negedge E) (0.033:0.033:0.033))

(HOLD (negedge D) (negedge E) (-0.064:-0.064:-0.064))

)

)

这个是我的sdf文件中的一部分

您解决了这个问题吗?我也遇到了同样问题哦。

之前在DC中出现过这个问题,DC/PT中没有报告时序违反,但是仿真的时候就是报告有setup的时序违反,后来发现是负载模型的问题