formality结果有问题,求助

时间:10-02

整理:3721RD

点击:

请教一下大神。我将自己的设计经过formality后,出现了unmatched点,和failing point。为什么是不一样的呢?

这大概要从什么方面去做啊,我这个设计有点大,结果出现验证不通过,有点茫然了

6 Unmatched points (6 reference, 0 implementation):

RefDFFr:/WORK/pc_top_no_speedup/Ucut_posi_2/cut_posi_reg[34]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_posi_2/cut_posi_tmp_reg[34]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_posi_2/cut_w_reg[2]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_posi_out_2/cut_posi_reg[17]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_posi_out_2/cut_posi_tmp_reg[17]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_posi_out_2/cut_w_reg[2]

---------------------------------------------------------------------------------------------------------------

20 Failing compare points (20 matched, 0 unmatched):

RefDFFr:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[0]

Impl DFFi:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[0]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[1]

Impl DFFi:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[1]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[2]

Impl DFFi:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[2]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[3]

Impl DFFi:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[3]

RefDFFr:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[4]

Impl DFFi:/WORK/pc_top_no_speedup/Ucut_2/dout_cut_i_reg[4]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[0]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[0]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[10]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[10]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[15]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[15]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[1]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[1]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[2]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[2]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[3]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[3]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[4]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[4]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[5]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[5]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[6]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[6]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[7]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[7]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[8]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[8]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[9]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_i_reg[9]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_r_reg[0]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_r_reg[0]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_r_reg[15]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_r_reg[15]

RefDFFr:/WORK/pc_top_no_speedup/Ufft_out_2/dout_r_reg[1]

Impl DFFi:/WORK/pc_top_no_speedup/Ufft_out_2/dout_r_reg[1]

--------------------------------------------------------------------------------------

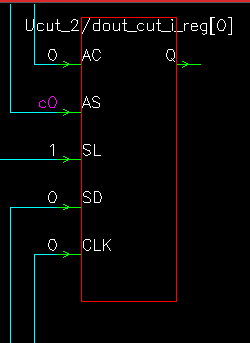

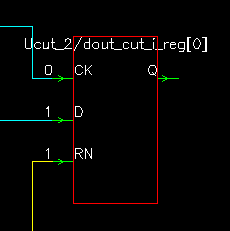

在查看电路图的时候,主要都是这样的:

ref:

Imp:

这是都是什么意思啊?

希望大神能指点迷经。感激万分

貌似 ref: scan Flip-Flop 不對應 Imp: Flip-Flop, 會不會是有做 DFT 的 design 與 未做 DFT 的 design 互比, 要用 set_constant 把 scan 的 pin Tie 0 試試看吧.

请问小编,这个问题怎么解决的?

其实主要是根据综合的网表来得到结果,做DC时,脚本设置的不同就会有不同的结果。当时是调用双口RAM时有的输入端口没用,然后我就空着没管,这样的话就会造成置1或者置0了,改了之后就好了。我的设计层次比较多,然后用去tri和去assign的语句后,网表中就没有DW了,结果也造成了formality不过的结果,这个不知道为什么,然后不去除tri和assign后,就通过了。还是要根据你自己的设计来看啦

小编,请问下 “网表中就没有DW了“你这里说的DW是指的DesignWare吗?

另外,我觉得按2楼的方法应该也可以通过的,不知道小编当时用2楼的方法做实验了没?

这个问题怎么解决的?