non-unate clock 处理方法

时间:10-02

整理:3721RD

点击:

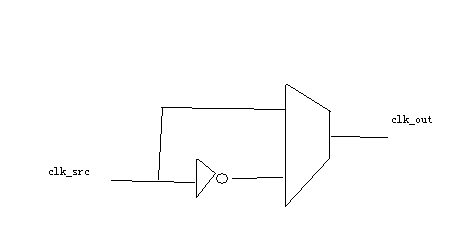

项目中有这样的逻辑

项目中有这样的逻辑clk_src 定义时钟后,DC 会报告non-unate clock ,确实需要正向与反向时钟都有,但是如果不做任何设置,clk_src 与取反的clk_src之间也会进行分析,这是不希望看到的,大家有没有更好的设置方法呢?

现在想到

1 反向时钟定义genearted clock,与clk_src 设置false path

2 两个sdc,不同case analysis

3将这种结构该为一个异或门,是不是更容易设置?

注:后面接的逻辑与其他时钟没有path,感觉只分析一种情况就好了(用一个case analysis),但是因为这种结构两种情况走的路径不同(一个经过反向器,一个没有),所以准确的话,应该都分析到,这样路径延迟才准确,如果用一个异或门代替这种结构,只有一条路径,是不是只分析一种情况就好了?

新手,虚心求教

cts把case给拿掉,或者对两端口设置动态平衡

定义2个clock clk_src, clk_src_n,

这两个时钟设置成两个group

把这两group设置成logical_exclusive

大家觉得如何?

如果你的_src周期够大,clk_src和 clk_src_n两个clock之间时序能满足

虽然clk_src和clk_src_n两个时钟实际上不存在timing 关系

多分析就让工具多分析下页可以的呀。

多谢!

这样的地方还挺多,我先按照您的方法处理与暂时别管这些做个对比,看看对综合结果有没多大影响,如果影响不大,就暂时先忽略了

多谢!

那按照您所说的第一种处理方法,CTS 时把case 拿掉,那ICC 是不是就会重新分析clk_src与clk_src_n之间呢?

第二种方法交给后端去处理,感觉挺好的,学习了! 再次感谢!