请教一个clock gating的问题,在线等

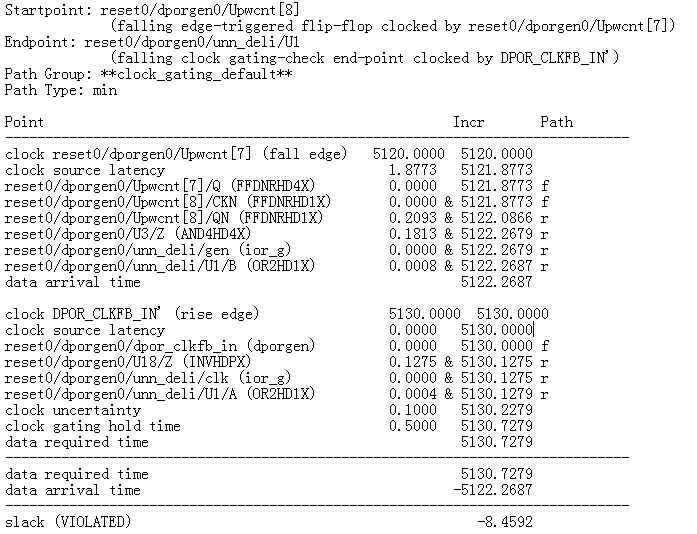

做完了Place & Route,没有发现问题。但是跑STA有一条violation,有几个疑惑:

1. clock DPOR_CLKFB_IN' (rise edge) 那 ‘ 是代表下降沿吗?

2. 这种检查对吗?

3.DPOR_CLKFB_IN的周期是20ns,为啥下面的clock pin是从5130开始?

4.因为上图中的FF都是低有效的,是不是把(OR2HD1X)改成AND gate会好一点?

5. 其实就是ripple counter,有人说不用做clock gating checking,对吗?

6. 我试着在Place & Route里用下面的命令报出这条path,但是没有找到路径,why?

> report_timing -to reset0/dporgen0/unn_deli/U1

No constrained timing paths found.

Paths may be unconstrained (try '-unconstrained' option).

新手盼望高手出现!

1. 是反相

2. 对啊 ,担心 glitch

3. 半个周期就是 10 ns 了

4. 只与 ior_g 有关吧

5. 不知道,也许吧

6. timing_check_defaults

4,为啥跟(OR2HD1X)没关系呢?那到底要改成And gate吗?

6,timing_check_defaults怎么用?

我是说跟前面的 flip-flop 什么边沿触发无关;

set timing_check_defaults gated_clock

set timing_check_defaults gated_clock

加了这个,还是No constrained timing paths found.

report_timing -to -delay minreset0/dporgen0/unn_deli/U1/A

这个命令只能在PT中报出路径,SOC中没有结果。

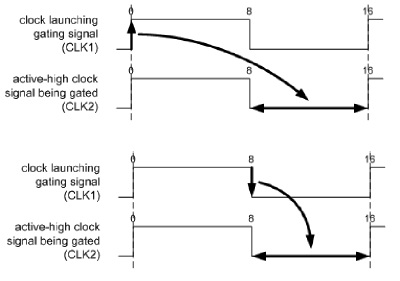

对照着How Are Clock Gating Checks Inferred.pdf这个文件,应该是我检查的起始点不对,如果改成从8ns位置的下降沿查hold time就没问题了。不知道分析得对不对?

create_clock -period 16 -waveform {0 8} CLK1

create_clock -period 16 -waveform {0 8} CLK2

这种计数器是异步电路,建议你做同步计数器取而代之。

做异步电路的工作量和风险高很多很多很多……。

怎么看出是异步的?我只是刚开始学做STA,别人的设计我改不了啊

如果做IC的话,数字电路能用同步就用同步,这是教条

你贴的那条CG的时序报告就是异步电路增加的额外工作量之一。

而且IC中的各种variation会对异步时序骚扰到死

同步or异步计数器参见:

http://wenku.baidu.com/link?url=U0Kl7WieT3sS59ym6nKL_IlvYAK5TxsjNqos0sH0zV49Dy06f1VfISyDmeZ1Bm_OrXkau078jk-KV1GsyM8YyyzBZngxGh3i5wF1I-SDUdK

http://wenku.baidu.com/link?url=vXJAxVEModoVbcOBHjsdEnaDrYMhGwaUdLW0O61yBdvDFwIRK9Jai4e-R5HbnyoJjQ_pzY22UGe_5mVm4bfUELgSfTN9RPzE_-_yAa1xKnO

我刚刚的回复被审核了没贴上?

百度一下ripple counter就知道了,IC中尽量不要用异步。

刚刚百度了一下,这种ripple counter都是异步的,是有点麻烦。但是设计已经是这样了,我怎么解决这个slack呢?

异步计数器的结构也各不相同的,比如增or减?最大计数值是多少?

你不贴源码,靠一个path可猜不出怎么解决这个问题。

依我看,你还是问问写代码的人比较靠谱:)

还有,真不改同步的话,恐怕生产出来的芯片不一定能用

学习了