vcs做后仿时,波形不稳定

时间:10-02

整理:3721RD

点击:

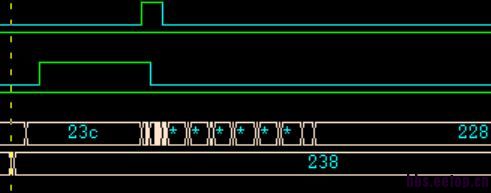

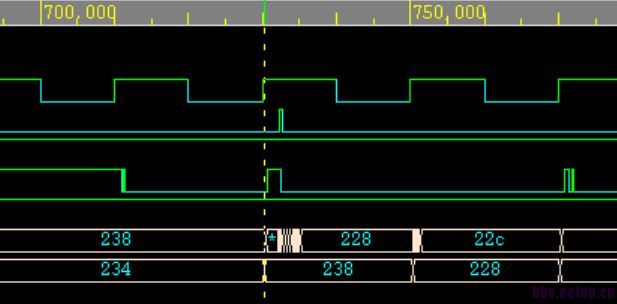

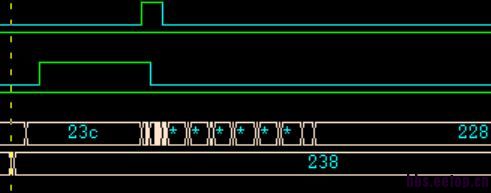

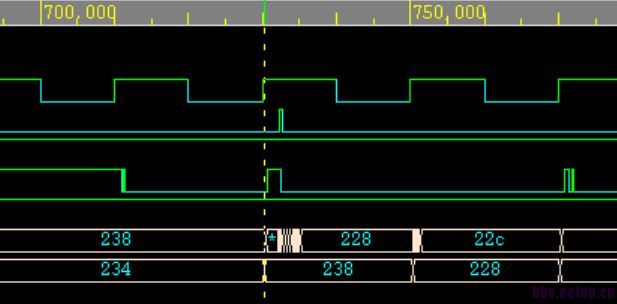

用vcs做后仿时,波形不稳定,会出现波动,使最后结果出现错误,下面是出错波形,望各位大神指点迷津!谢谢啦!

这个需要调试的, sta过了么,margin大么

你好,先谢谢你的及时回复。这个还没做sta,sdf也是dc生成的,不是由版图提取的,就是想先看看网表文件在有延迟时,功能是否正确,如果正确在把网表文件 给后端进行后续工作,因为刚学做后仿,纯菜鸟,我怕是因为我vcs的某些参数设置不合理导致这个问题,因此,请大神帮帮忙!多谢!

通常等sta,fm过了再后仿真的,timing如果不行,当然没法出波形的

`h238至少是10bit的总线,对应逻辑中是独立的10条路径,延时不同,先后到达,导致波形看上去不对齐。正常。

你说的错是`h23c 到达晚了,没有被正确采样吗?

时钟频率多少呢?