多个时钟balance的问题

时间:10-02

整理:3721RD

点击:

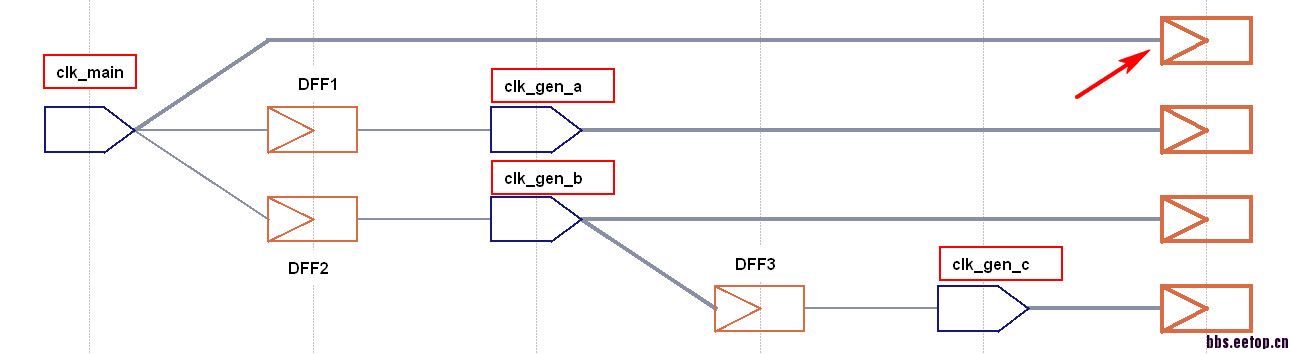

时钟树的结构如图所示,如果我不想balance红色箭头所指的DFF,其他三组之间需要balance。那么SDC和exception有几种写法呢?

对于clock balance不懂,同问~

帮顶!

能写一种不就好了,

都是同源clock,都balance不就好了么,

红色箭头指的DFF很少,只有几个。而其他时钟树下面的DFF较多,每个时钟树大约一万多sinks。一起balance会让红色箭头指的DFF的时钟树的latency过大。

过大又有什么问题么?timing ?

正规做法就是设 exclude pin不就好了

会有timing问题。exclude pin 怎么设置好些呢?

是将这些DFF都设exclude pin?还是手动插个buffer,将buffer设为exclude pin?

就将红箭头那个flipflop的clock pin设成exclude pin,其他的正常做cts就好了

红箭头指的是一组DFF,那么将他们的CK pin都设置为exclude pin 吗? 谢谢。

是啊, 自己试啊,别小马过河,畏手畏脚的,很多都是自己尝试做出来的,别人没法帮你到底的

好的,谢谢版大!