STA所需读入的文件

请求帮助

我所知道的一般是输入:网表,sdc,spef(或其他RC参数文件),library的db 文件就可以了。输出文件sdf,网表,拿来做后仿真。

你说的是在PT里面进行STA时是在ICC提取的文件sdf、spef任选其一就行对吧?,那用哪一个比较准确一点呢?

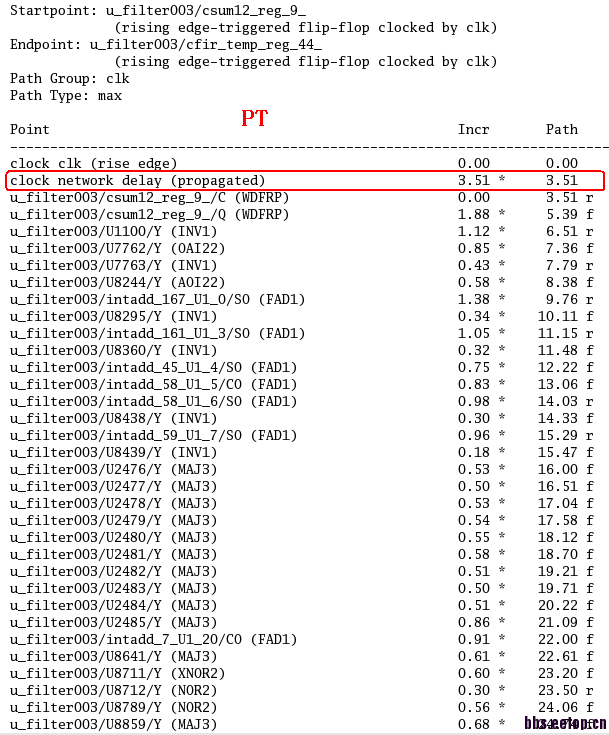

我还有一个问题就是在ICC里直接进行时序报告与提取的sdf进行时序报告,如图中,产生的时钟延时(红框内画出)为什么会有那么大差别,是因为它们各自软件的环境不同还是什么原因?

读SPEF,吐出SDF给后仿用

从你的报告看,PT读入的是SDF。

从signoff角度,PT读入的是从StarRC抽取的SPEF文件(可以分析SI,Noise等),若SDF文件,仅仅是返标的过程,只能看delay。

ICC和PT的报告不同建议你打开type_path full_clock_expanded,以及transition,capactiance等选项。比较具体cell,net的属性。

现在的PT和ICC版本,PT要乐观一些。

同意6#

哦,明白了,谢谢!

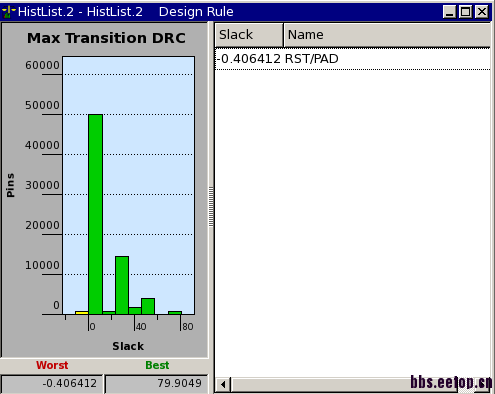

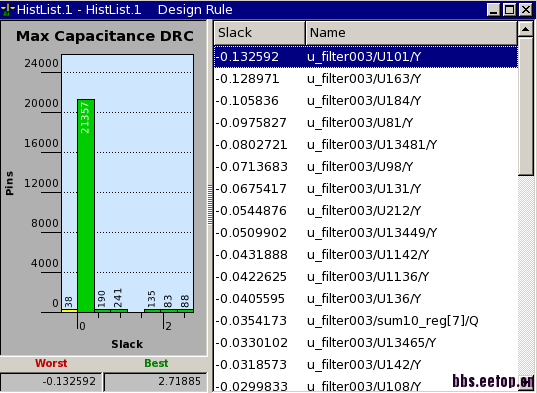

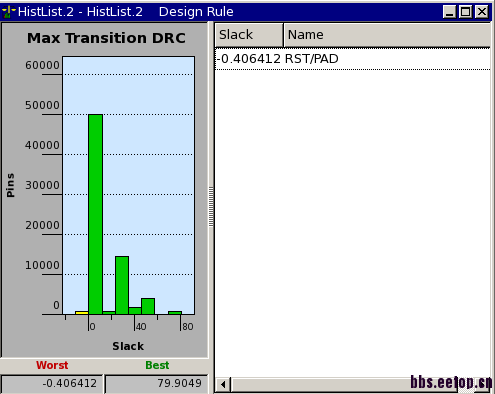

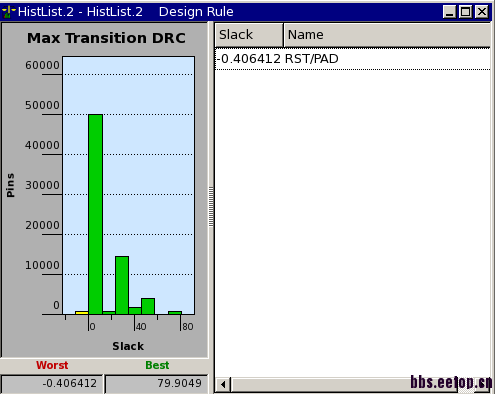

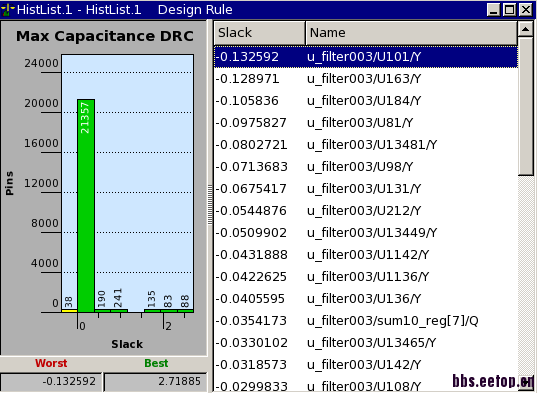

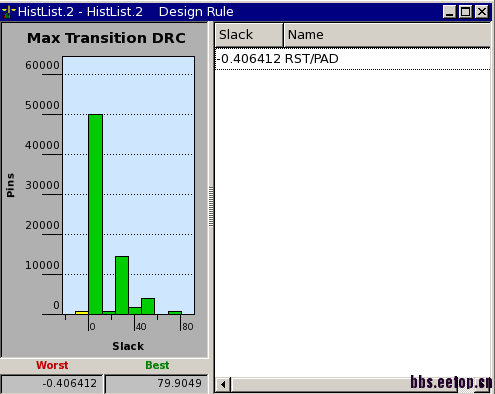

我还想请问一个问题,我在ICC里面report_constraint -all_violators,没有出现max capacitor、max transition的design rule违例,而在用SPEF文件读入PT做静态时序分析后报告会有如下图所示的max capacitor、max transition的违例,而且max capacitor还是出现在内部的一些单元的输出端口,请问这是什么原因,有什么解决办法?

哦,明白了,谢谢!

我还想请问一个问题,我在ICC里面report_constraint -all_violators,没有出现max capacitor、max transition的design rule违例,而在用SPEF文件读入PT做静态时序分析后报告会有如下图所示的max capacitor、max transition的违例,而且max capacitor还是出现在内部的一些单元的输出端口,请问这是什么原因,有什么解决办法?

哦,明白了,谢谢!

我还想请问一个问题,我在ICC里面report_constraint -all_violators,没有出现max capacitor、max transition的design rule违例,而在用SPEF文件读入PT做静态时序分析后报告会有如下图所示的max capacitor、max transition的违例,而且max capacitor还是出现在内部的一些单元的输出端口,请问这是什么原因,有什么解决办法?

哦,明白了,谢谢!

我还想请问一个问题,我在ICC里面report_constraint -all_violators,没有出现max capacitor、max transition的design rule违例,而在用SPEF文件读入PT做静态时序分析后报告会有如下图所示的max capacitor、max transition的违例,而且max capacitor还是出现在内部的一些单元的输出端口,请问这是什么原因,有什么解决办法?

图片如下

请问可能会是什么原因造成的,都无从下手啊

顶一个。学习了。

这是ICC与PT之间的一致性,首先你可以在ICC中执行check_signoff_correlation看看是不是存在参数设定的不同。

SPEF如果直接从ICC写出应该不会有什么差别,如果经过STAR RC的话,建议你查一下STAR RC的脚本,比如MODE的设定值等。

另外ICC中是否已经插入dummy metal?间距的设定是否合理。约束文件是否相同?

ICC和PT现在的correlation已经很好了。不应该有太大的差别。同意15#,而且只从贴图信息量太少,根本看不出原因。

请问在PT里怎样输出网表?我一直都是在PT里做了ECO之后,回到网表手动修改。

应该不是这个原因,因为我用ICC中写出的spef文件读入PT中一样有这个违例

违例的原因应该是因为在违例端口插入的BUF驱动能力太小,例如图中的u163/Y这个端口后并没有接入BUF,它后面所接寄存器的总的负载电容值为1.14pF,而u163为BUF3,库中BUF3的max capacitance为1.02pF,所以就出现了-0.12的违例,但是这个插入的BUF是自动插入的,我该怎样使得它插入的BUF驱动能力更强?

ICC中并不报告违例,是否认为只要插入BUF3就ok了

谢谢size_cell.

PT eco 的时候会考虑transition的(参考fix_timing_eco的相关选项)。已经解决了,谢谢各位

学习了