求助generated_clock与source clock之间的timing问题

时间:10-02

整理:3721RD

点击:

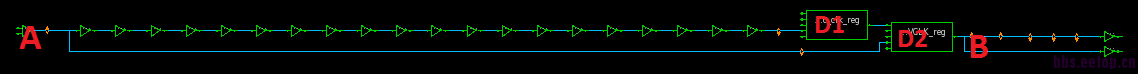

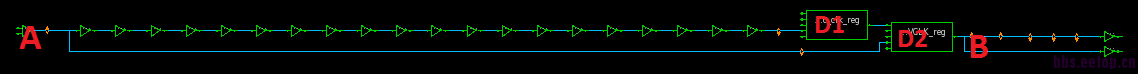

如图,A 为master clock, B为generated clock, 为了balance A与B之间的skew, D1之前加了很多个buffer,但D1和D2之间又有时序约束,导致timing violation很大。请教各位大侠,有什么方法可以让icc 不去balance A和B吗?谢谢~

设D1的pin为non_stop_pin 试试吧

谢谢!

我试着把D2的CK端设置为stop_pin就可以balance了。