对 master 和 generated clock 需要设不同的 uncertainty 值吗?

时间:10-02

整理:3721RD

点击:

如果设计里有多个时钟,那么fab给uncertainty或者setup hold margin的时候,是针对每个时钟给一个吗 还是只给一个?

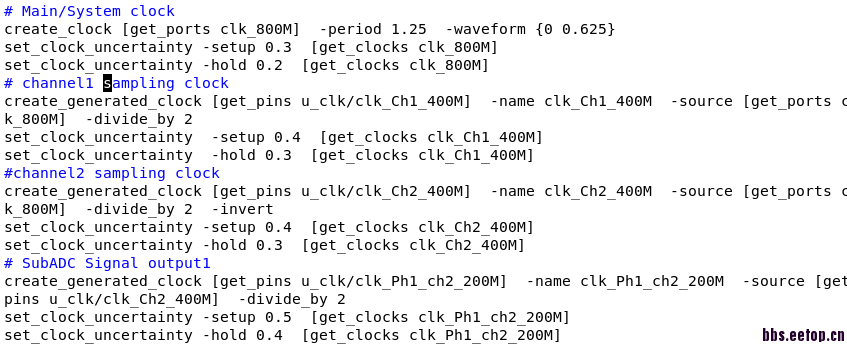

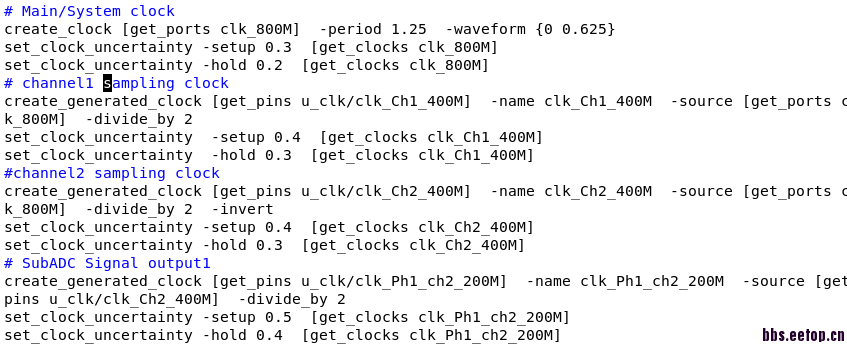

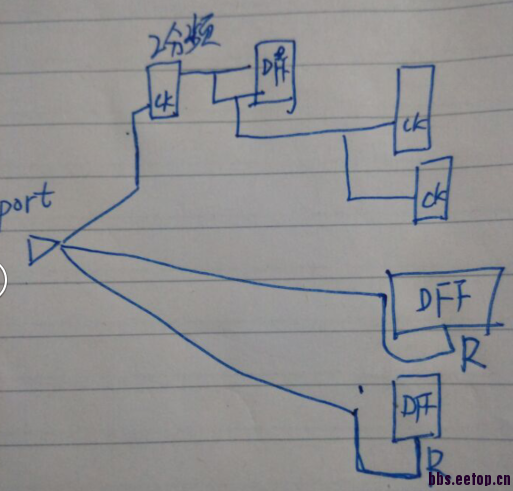

如下图:

对 master 和 generated clock 需要留不同的 uncertainty 值吗?

如下图:

对 master 和 generated clock 需要留不同的 uncertainty 值吗?

通常是一个比较方便, 也可以多个用于分别控制

版大,你以前做的项目中,fab给的uncertainty或者setup/hold margin一般留多少呢?是时钟周期的百分之多少一般?

如果master clock是1.25ns,generated clock是2.5ns,这样的话 master 和 generated clock 的margin就不一样了,

generated clock留的margin要大些项目中是这样的吗

一般500M以上设一个值500M以下设一个值每个时钟都设挺麻烦的主要还是要看pll的jitter有多大,电源打的够不够

(1) 时钟频率越大,留的margin越大还是越小?

(2)我觉得对于master clock 和 generated clock 来说,PLL产生的 jitter 都是一样的,都是时钟源到寄存器

到了公司会有人告诉你的, 不是啥都需要提前知道的,

饭都是一口一口吃的,