clock source 为什么不能定义在hierarchy pin上呢

Clocktreesynthesis(CTS)requiresthatclock sources must be at points that have physical information.In general, a hierarchical

pin doesnothavephysicalinformation for accurately calculating clock delay;

想问下,什么是hierarchy pin?为什么老版本icc中不能将clock source建在hierarchy pin上?

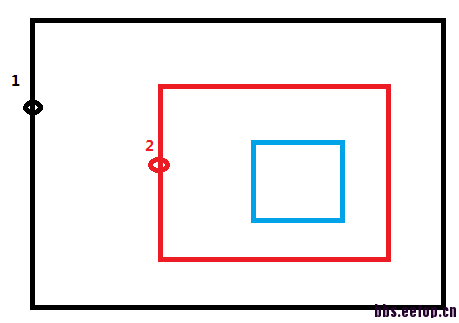

上图中1是input port,2 应该是一个 internal hierarchy pin 吧? 为什么可以将 clock source 定义在 input port上,而不能定义在 2上呢?

你能不能找出这个hierarchiy pin的物理位置?以及如何计算这个点之后的net的delay值?

我可能对hierarchy pin理解的不对;

如果黑色方框是我的block,蓝色方框代表一个stand cell,那么红色方框可能会代表什么呢?

hierarchy pin会在后端的过程中被优化掉,连pin都没有了,那这个时钟还设的上么?

如果黑色方框是我的block,蓝色方框代表一个stand cell,那么红色方框可能代表一个macro,请问macro的pin怎么可能会在后端被优化掉呢

文章里面写的很清楚,hierarchichy pin是没有物理信息的。

红色的是属于hierarchichy pin, 但是他也只是逻辑上存在,物理上没有一个确定的的点 (x, y)和他对应。

假设红色方框是macro,那么我一旦将macro fixed,那么这个macro上任何一个pin (hierarchy pin) 的位置,我就可以确定啊 [用(x y)确定]

你之前一直说的是hierarchy pin 怎么又扯到macro pin了,这是两回事好不好,macro pin就是一个物理上存在的pin,不是hierarchy pin,hierarchy pin是逻辑上存在而物理上不存在的,只是前端代码里一个module的pin,还有,你说蓝色是stdcell ,红色又怎么可能是macro

macro里还不是由stand cell构成的吗?

恩,你说的意思我明白了;比如有 top.va.v b.v c.v每个 .v 文件中是一个 module,假设 a.v 调用了 b.v , b.v 又调用了 c.v 那么

b.v 的这个module的pin,就是逻辑上存在的,就是个hierarchy的pin;你说的是这个意思吧

13版的icc中,只要上面那个变量设置为true,就可以将clock source pin设置再hierachy pin上,那么此时工具又是如何计算这个pin之后net 的delay呢

man一下这个variable最后一句就是了

It is for designswithclock sources or clock exceptions defined at hierarchical pins

The clock source is assumed at a pin of the top-most buffer inserted by the tool

你说的是哪句,我man了之后,还是不太明白;