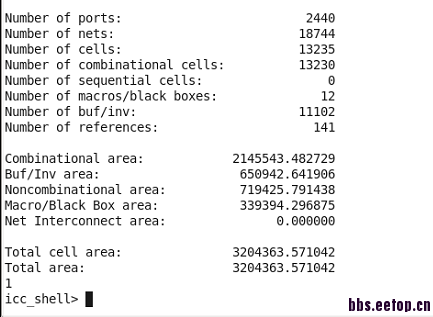

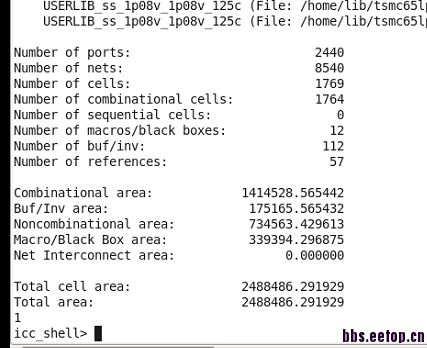

place 之后cell 数量一下曾大很多 一般会这样么 如图

时间:10-02

整理:3721RD

点击:

report_design -physical 看看, place完了会增加20~30%的cell instance count的

3q 大侠

主要是 利用率 一下子 从65% 窜到了 85%

Check how many buffers have been added (11102-112=~11000), that may be caused by many many HFN (high fanout net) in your synthesize netlist.

2 reasons I can imagine:

(1) poor qualify of synthesize netlist. (Maybe max_fanout, max_cap or WLM are not set correctly)

(2) poor floorplan causes a lot for detour in trial route, which increases estimated wireload and buffers are needed by the tool.

I would check the (1) first.

FYI.

膜拜了 大神 前端 release 网表 确实问题很多而且时序离约束差的很多floorplan的话design logic 比较简单sram种类也很少 我再跟 fe沟通下 3q