DC中的wire_load_model问题?

时间:10-02

整理:3721RD

点击:

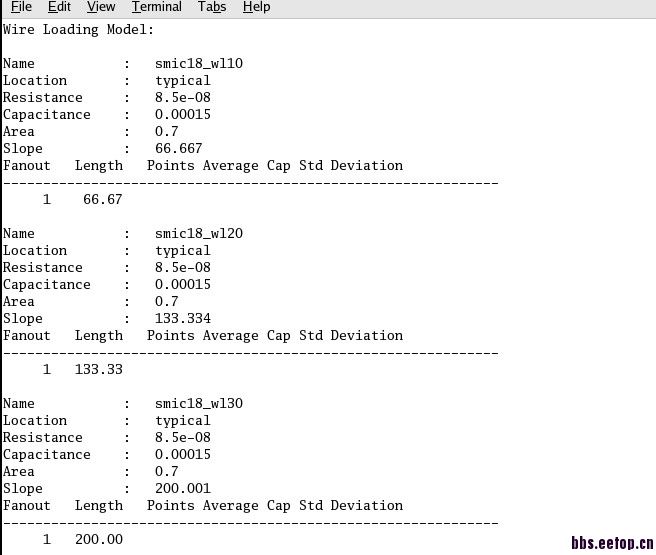

在做DC综合写约束时,里面遇到了点问题。如何选择wire_load_model?有类似一下的模型Wire Loading Model:

Name:smic18_wl10

Location:typical

Resistance:8.5e-08

Capacitance:0.00015

Area:0.7

Slope:66.667

FanoutLengthPoints Average Cap Std Deviation

--------------------------------------------------------------

166.67

Name:smic18_wl20

Location:typical

Resistance:8.5e-08

Capacitance:0.00015

Area:0.7

Slope:133.334

FanoutLengthPoints Average Cap Std Deviation

--------------------------------------------------------------

1133.33

该怎么选呀?

还有就是smic18_wl20中的wl20中的是什么意思?20是有多少门吗?那20的单位是什么?

小妹刚刚做综合,求大神帮助呀呀呀?

还有个问题就是wire_load_mode中的Top,enclosed,segmented这三个怎么选呀?

Name:smic18_wl10

Location:typical

Resistance:8.5e-08

Capacitance:0.00015

Area:0.7

Slope:66.667

FanoutLengthPoints Average Cap Std Deviation

--------------------------------------------------------------

166.67

Name:smic18_wl20

Location:typical

Resistance:8.5e-08

Capacitance:0.00015

Area:0.7

Slope:133.334

FanoutLengthPoints Average Cap Std Deviation

--------------------------------------------------------------

1133.33

该怎么选呀?

还有就是smic18_wl20中的wl20中的是什么意思?20是有多少门吗?那20的单位是什么?

小妹刚刚做综合,求大神帮助呀呀呀?

还有个问题就是wire_load_mode中的Top,enclosed,segmented这三个怎么选呀?

随便选,没太多关系

那smic18_wl10后面的10是什么意思?

只是模拟fanout的大小吧, 搞那么清楚干啥呢,先run还行?

还有还有问题,就是对于同一个电路,我加的约束也是一样的,但是compile几次之后,第一次和第二次compile之后的slack为什么会不一样呢?

是这样的, 多玩几遍就有感觉了