create_generated_clock用分频器

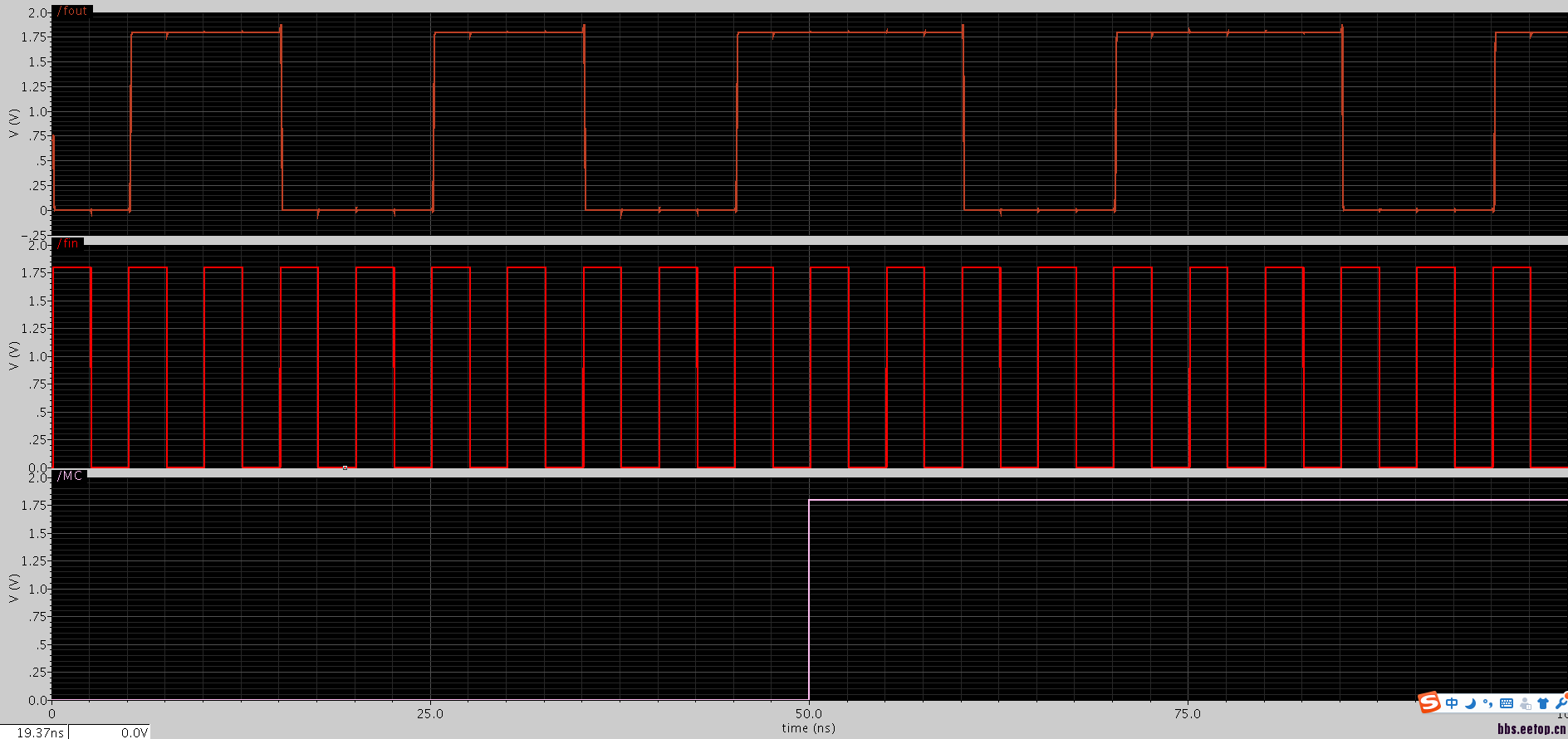

这个经预分频后的时钟fout送给ps计数器作时钟输入,然后再得到ps计数器的输出fdiv用来给后面的模块做时钟使用,像这种情况如何利用create_generated_clock做时钟约束啊?

创建2个generated clocks, 用-add 来叠加

小编,是这样产生clk_ps_counter和clk_div这两个时钟给后面使用吗?另外需不需要给clk,clk_ps_counter,clk_div这三个时钟相互设置flase_path?

最后问问什么情况下需要对时钟使用set_dont_touch_network?为什么?

谢谢小编。

create_clock -name clk -period 1 [get_ports clk]create_generated_clock -name clk_ps_counter -divide_by 4 -source [get_ports clk] [get_pins ../Q] -master_clock clk -add

create_generated_clock -name clk_div -divide_by 10 -source [get_ports clk] [get_pins ../Q] -master_clock clk -add

create_clock -name clk -period 1 [get_ports clk]

create_generated_clock -name clk_ps_counter -divide_by 4 -source [get_ports clk] [get_pins ../Q] -master_clock clk -add

create_generated_clock -name clk_div -divide_by 10 -source [get_ports clk] [get_pins ../Q] -master_clock clk -add

对, 主时钟和分频时钟是同一个domain的,没必要设false path