什么是 chip utilization

core utilization应该指的是 core的面积与chip的面积之比;那么chip utilization指的是 chip的面积和谁的面积之比呢,我看网上说:Chip utilization depends on

Standard cells macros and IO pads;

请解释下chip utilization 吧

这种问题你可以试着输入几个值就知道了,输入0.8跟输入0.4,比较一下初始化floorplan版图就知道了。

尽量自己探索,嘿嘿。

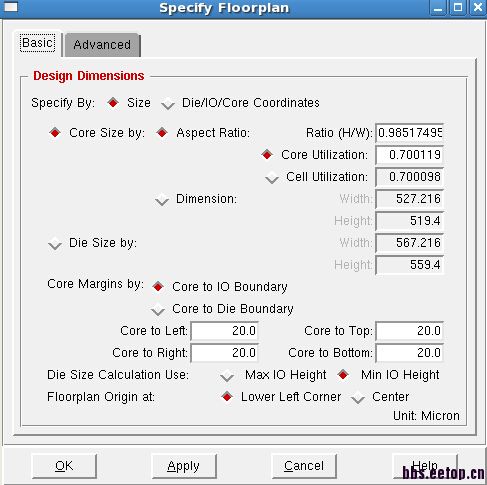

你说的是从哪儿输入啊 ,这里只有core utilization没有chip utilization啊

Placement area utilization, or simply “utilization,” means the percentage of area available for placement that is already occupied by placed cells. For example, a utilization of 80 percent means that 80 percent of the available area is occupied by cells and 20 percent is empty and can still be used for additional cell placement, for movement of cells for legalization and optimization, or as an allowance to prevent excessive routing congestion.

(non-fixed_standard_cell_area + fixed_standard_cell_area) / (total_area – blocked_area)

出自何处,我觉得不对啊,或者这么说吧total aree指的是什么,我知道的是

chip area=core area+power ring area+PAD ring area

请问你那个total area指的哪里

手册上有说:

Core Size = (standard cell area/core utilization) + (macro area + halo)

那我之前理解的core utilization是错误的,应该是标准单元面积与core面积之比(假设只有std cell,没有macro和halo),那chip utilization应该指的是 (core area+power ring+PAD ring)/chip total area