一个时序优化的问题

时间:10-02

整理:3721RD

点击:

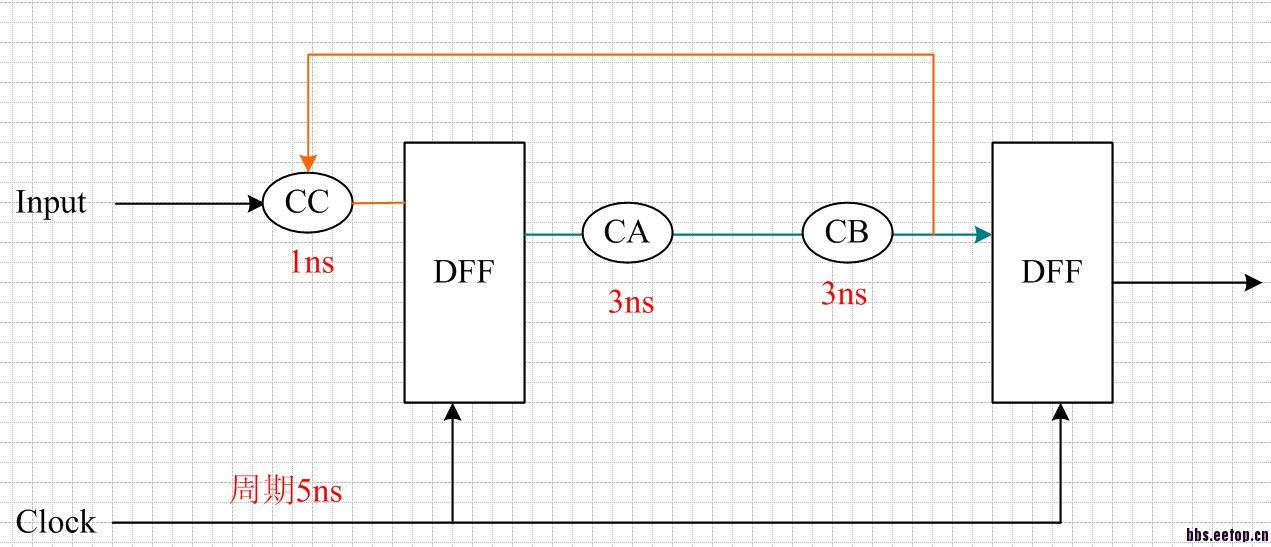

如图,两条path的timing 都不满足。

要求修改rtl,在不影响功能的前提下,满足时序。

我觉得这个是无解的。有高手知道吗?

调cts skew啊, useful skew用下

感谢回复。这个方法是可以用的。

但是出题目的人说是修改rtl code可以做到。我是想不到方法了。

可不可以在CA和CB中间加个reg?

别告诉我是把CA挪到第一个DFF前面去...

我认为应该是不行的,第一个DFF有个loop。这个要一拍做完,前后有依赖关系。

有两条Path出现setup违例:

一条从DFF1的CK端到DFF2的D端,可通过useful skew解决;

一条从DFF1的CK端到DFF1的D端,不可通过useful skew解决,因为launching clock 和capture clock一样,不存在skew。

在CA、CB之间插入寄存器DFF3。为确保功能正确,在INPUT后插入寄存器DFF4,使得CC的两个fanin被延迟同样的周期数。

这样,DFF2的输出会比改之前推迟2个周期。其中复位后前2个周期的数据是多余的,其后的数据是改之前的2个周期delay。

以上分析,请实验验证。--------

刚用积分器进行了Z变换信号分析,不对。

中间用个负沿latch?

哈哈,最后一句话是对的。

第一个DFF的loop,3段组合逻辑之间有依赖关系。如果弄成多拍,会影响功能。

我也想到了这个,可以借一点时间。

我怀疑出题目的人,自己都搞不清楚。