Latch中关于 max_borrow_time的问题i

时间:10-02

整理:3721RD

点击:

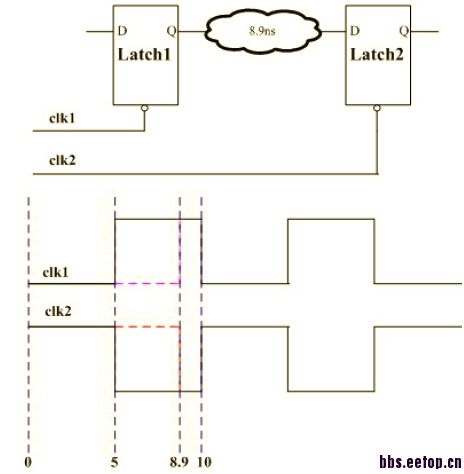

上图是基于latch的设计,黑色时钟线代表没有borrow time的时序图,粉红和红色部分代表borrow time。

对于latch2进行建立关系检查。由于logic的8.9ns的延迟,latch1输出至少要经过8.9ns的时间才能到达latch2。但是根据时序图可以知道clk1,和clk2的关系,当latch2 capture 数据的时候,latch1的数据还没有到。这样就会产生逻辑故障。

为了修正这个逻辑故障,综合工具会borrow time,以满足建立时间关系,如上图中的红色和粉红色部分。综合工具会使clk1的低电平持续的时间够长,那么就要使clk2的低电平够端,只要满足setup relation就可以。

如果latch2还有下级,那么我们可以知道,由于上级的borrow time,下级有可能会产生一些time violations。

这个时候我们就要用set_max_time_borrow 限制综合工具借入更多的时序,为了满足setup relation,综合工具会最大优化logic部分。

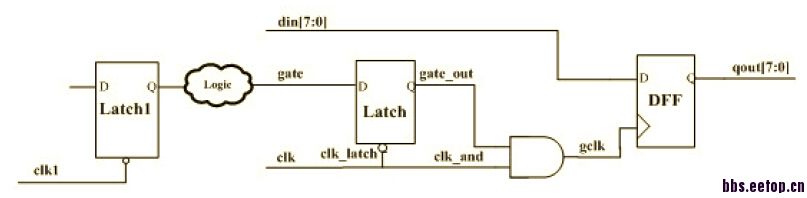

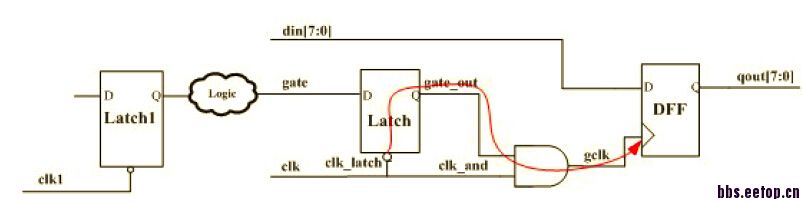

如果将上图放入到门控电路中,如下:

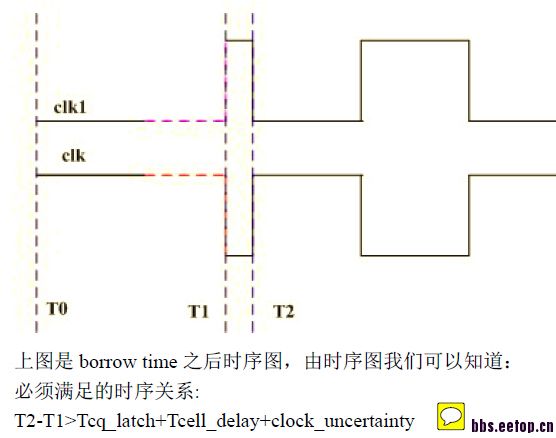

结合borrow time的时序图,我们分析下门控时钟里面可以设置的最大borrow time:

我想问下 T2-T1为什么还要大于 与门 的延迟呢? 不是在Latch透明期间,将Latch的输出送到与门的输入就行了吗?

求解释

内容因为T2那时DFF就一定要得到数据才行

哦,我知道你的意思了,我说错了,确实好像clock gating check 不用这个and的cell delay哎

恩,确实不用的,可能作者笔误 写错啦