clock gating cell的hold time violation问题

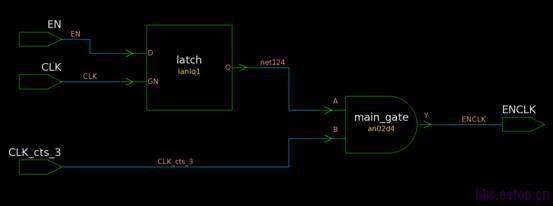

做完P&R以后,抽取完寄生参数,放到PT中做STA,发现clock gating cell中的main gate(and gate)的A,B两个

端口报hold time violation,A口是CLK和EN信号经过一个latch,B口是CLK信号,但是是经过CTS以后的clk,网络

名为CLK_cts_3(请见附图1)。但是A口的信号比B口的信号早到,于是 PT报了hold time violation,请问这种问题

是应该在ICC中加约束把violation修掉,还是有其他的处理呢?先谢过各位各位大侠了

================================= PT给出的具体的Timing Report =============================

Startpoint: Controller/clk_gate_i_reg/latch

(negative level-sensitive latchclocked by clk_4_div)

Endpoint: Controller/clk_gate_i_reg/main_gate

(rising clock gating-checkend-point clocked by clk_4_div)

Path Group: **clock_gating_default**

Path Type: min

PointIncrPath

------------------------------------------------------------------------------

clock clk_4_div (fall edge)140.00140.00

clock network delay (ideal)2.84142.84

Controller/clk_gate_i_reg/latch/GN (lanlq1)0.00142.84f

Controller/clk_gate_i_reg/latch/Q (lanlq1)0.18143.02 r

Controller/clk_gate_i_reg/main_gate/A (an02d4)0.00143.02 r

data arrival time143.02

clock clk_4_div (fall edge)140.00140.00

clock network delay (ideal)3.09143.09

Controller/clk_gate_i_reg/main_gate/B (an02d4)143.09f

clock gating hold time0.00143.09

data required time143.09

------------------------------------------------------------------------------

data required time143.09

data arrival time-143.02

------------------------------------------------------------------------------

slack(VIOLATED)-0.07没错,这个是典型的 离散icg (discrete) 类型, hold violation是真的

以pt结果为主吧, 再修下就好了, 加buffer

谢谢ICFB大

还想问清楚一点,就是这个在ICC里面怎么具体修呢?是针对报HOLD VIOLATION的几条路径逐条加BUFF, 还是用其他的方法?我在CTS后使用

clock_opt -fix_hold_all_clocks

修过大部分路径了,有可能是其中修CLK_cts_3这条路径加BUFF太多增加了太多DELAY,我现在的修hold的时候加的uncertainty是1ns, 我改小到0.5ns但是不起作用,请教具体该怎么修呢?

在CLK这条path上加buffer.

我是觉得如果你的clock不多,也不复杂的话, clk skew有250ps,已经有点偏大了.

如果用ICG的话,根本就没有这个问题了。因为前面的latch已经保证了main_gate的时序

少量的hold violation,把所有endpoint 找到,直接insert_buffer就行了,很快的

你不能指望icc能把所有的hold clean 掉, 总会有顾此失彼的时候,

小编,他这个PR后怎么clock 还是ideal的?

也是啊,你设了 set_propagated_clock么

从数值看不像是 ideal的,

请教陈大,foundry提供的库里面其实是有专门的clock gating cell,但是在DC综合里面我用以下的脚本:================================================================

set_clock_gating_style -sequential_cell latch -positive_edge_logic {and} -negative_edge_logic {or}

insert_clock_gating

propagate_constraints -gate_clock

================================================================

来做门控时钟的综合约束,所以估计才生成了离散的门控时钟单元,那在DC里面怎么样设置才能使得DC综合时针对

上升沿和下降沿的时钟能够自动调用foundry库里提供的门控时钟呢?

icfb大,我在PT里面设置了set_propagated_clock [all_clocks],但是在这之后又定义了几个create_generated_clock,不知道是不是propagated这个属性没有设置到后面定义的clock上去呢?

当然是先定义所有clock,然后再 set_propagated_clock 啊,

set_clock_gating_style -pos integrated -neg integrated

吧,你看看manual,很清楚的

你选or,and,当然是综合成离散icg啊,

set_clock_gating_style -sequential_cell latch -positive_edge_logic {icg_cell_name}

多谢涛大和ICFB大的解答,我用

set_clock_gating_style -sequential_cell latch -positive_edge_logic {integrated:/lib_name/icg_cell_name}

编译时可以成功调用库中的ICG了,但是set_clock_gating_style中的-negative_edge_logic的设置我不是特别理解, 是用来设置哪种情况的呢?

一般就是用一种icg吧, 就是上升沿或者下降沿来gate, 没有必要pos,neg都用,

谢谢解答,来学习。

换成ICG后 EN端可能就会有setup问题了 这个比hold要难解的多

请问在DC综合的时候,用什么命令让DC把那条路径(小编贴出来的那条有hold violation的路径)report出来呢?

DC的时候,时钟还都是ideal的,估计报不出来吧,就算报出来也没有用啊。这些hold violation都是在DC之后修的呀。

ICG cell可以解决问题。

也可以用timing borrow的方式去解决。

学习中