CTS后DRC violation无法修复,显示dont_touch

NetFanoutFanoutSlack

-----------------------------------------------------------------

CLK_G1B12I84 (dont_touch)

15.0035.00-20.00(VIOLATED)

CLK_G1B12I119 (dont_touch)

15.0035.00-20.00(VIOLATED)

CLK_G1B12I136 (dont_touch)

15.0035.00-20.00(VIOLATED)

CLK_G1B12I149 (dont_touch)

15.0035.00-20.00(VIOLATED)

CLK_G1B12I165 (dont_touch)

15.0035.00-20.00(VIOLATED)

CLK_G1B12I178 (dont_touch)

15.0035.00-20.00(VIOLATED)

CLK_G1B12I55 (dont_touch)

15.0034.00-19.00(VIOLATED)

CLK_G1B12I63 (dont_touch)

15.0034.00-19.00(VIOLATED)

CLK_G1B12I133 (dont_touch)

15.0034.00-19.00(VIOLATED)

CLK_G1B12I168 (dont_touch)

15.0034.00-19.00(VIOLATED)

CLK_G1B12I179 (dont_touch)

15.0034.00-19.00(VIOLATED)

u2/CLK_G1B12I147 (dont_touch)

15.0034.00-19.00(VIOLATED)

CLK_G1B12I102 (dont_touch)

15.0033.00-18.00(VIOLATED)

CLK_G1B12I105 (dont_touch)

15.0033.00-18.00(VIOLATED)

CLK_G1B12I141 (dont_touch)

15.0033.00-18.00(VIOLATED)

。

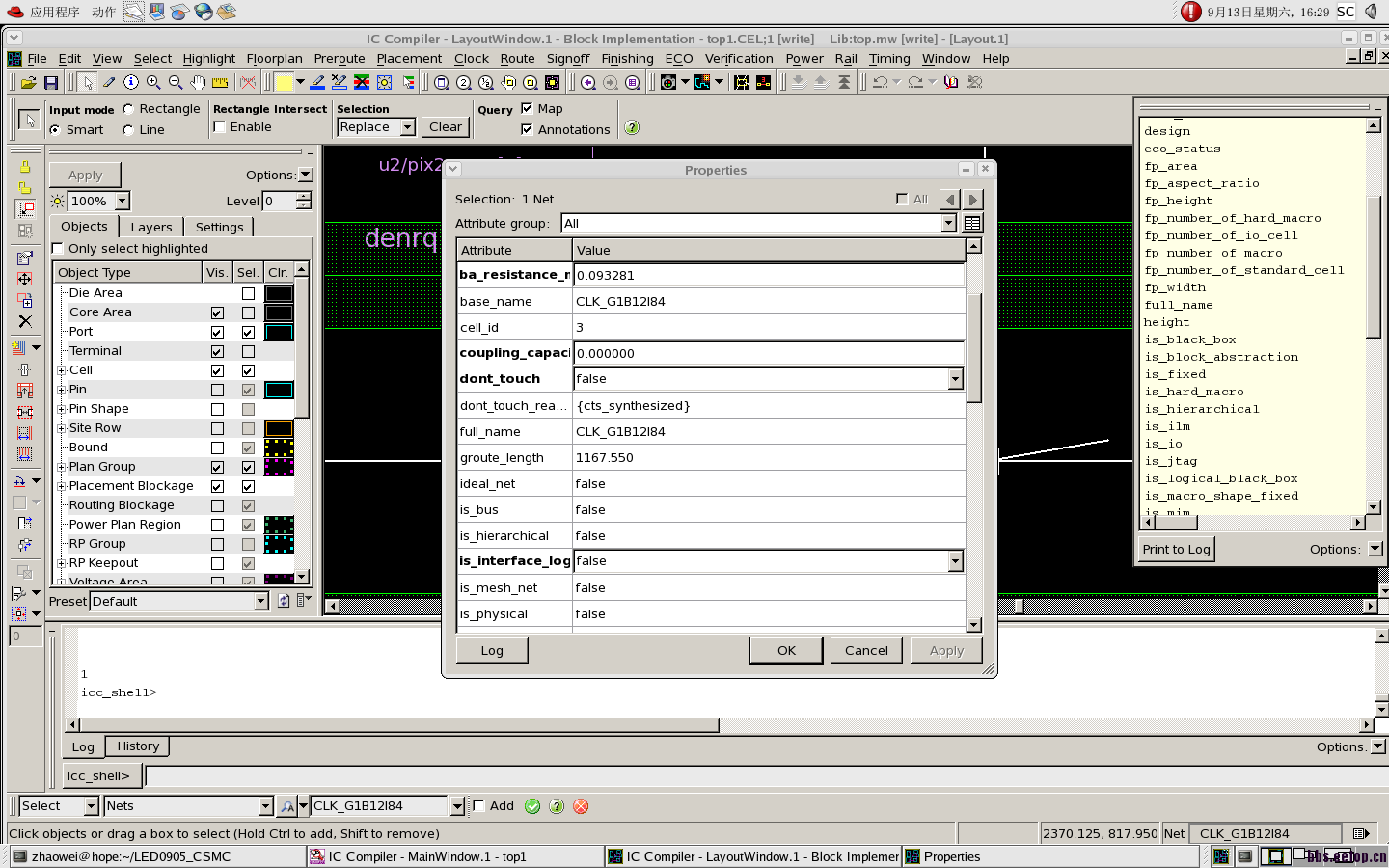

我在其中选择了一个net 然后ctrl+R看到其属性中的dont_touch是false的,如下:

chrt035工艺没有出现过这种情况,现在用的是CSMC035工艺,脚本是一样的。ICC工具为什么认为是dont_touch呢?求前辈指点!谢谢!

chrt035工艺没有出现过这种情况,现在用的是CSMC035工艺,脚本是一样的。ICC工具为什么认为是dont_touch呢?求前辈指点!谢谢!

综合网表里怎么设置max_fanout的?

remove_ideal_network

set_max_fanout 32 [current_design]

logical

综合时候没有设置max_fanout,ICC做apr的时候这个constraint应该是从logic library来的吧,是必须要满足的吧

这个命令我用过了,做完以后还是上面这种情况。我的CTS命令如下:remove_clock_tree -clock_trees CLK

remove_ideal_network -all

set_propagated_clock [all_clocks ]

set_input_transition -max -rise 0.5 [get_ports CLK]

set_input_transition -max -fall0.5 [get_ports CLK]

set_input_transition -min -fall0.5 [get_ports CLK]

set_input_transition -min -rise0.5 [get_ports CLK]

set_clock_tree_options -max_transition 0.5

set_app_var cto_enable_drc_fixing true

set_clock_tree_options -target_early_delay 0.7 -target_skew 0.2

remove_clock_tree -clock_trees CLK

define_routing_rule MY_CLK_RULE -widths {METAL1 0.6 METAL2 0.6 METAL3 0.6 METAL4 0.6} -multiplier_spacing 2.0

set_clock_tree_options -clock_trees [all_clocks ] -routing_rule MY_CLK_RULE

set_clock_tree_options -use_default_routing_for_sinks 1

clock_opt -no_clock_route -only_cts

set_propagated_clock [all_clocks ]

update_clock_latency

report_clock_timing -type skew

report_clock_timing -type latency

set_fix_hold [all_clocks ]

extract_rc

clock_opt -only_psyn -no_clock_route -area_recovery

route_zrt_group -all_clock_nets -reuse_existing_global_route true -stop_after_global_route true

extract_rc

report_constraint -all_violators

您好!我对比了下之前用相同命令用chrt做的layout,发现原来做的时候CLK网络的dont_touch是unknown,我把这个属性移除掉再试试

.35 um 工艺需要 fanout limit为15么,太小了吧,50都行,

跑的很慢的,

小编您好!我改成50再试试,不过就是不太明白为什么工具给出了(dont_touch)属性,因为在看属性的时候这个选项已经是false了。我觉得可能是因为dont_touch的问题导致了max_fanout违约。

需要在设计placement之前去掉dont_touch.

您好!我在placement之前用了这个:remove_attribute [get_nets * -all] dont_touch 但是做完CTS之后还是有max_fanout违约,提示和之前是一样的。

有这个是正常的。修修嘛。在SOCE下,set fixFanoutLoadMode true optDesign -postCTS -drc

我用set_clock_option -max_fanout 15之后就没有fanout violation了。我用的是ICC,SOCE不是很懂,不过命令是类似的,我也用类似的命令修过,不过还是修不动,工具会报dont_touch

LZ你做完cts clock tree 会被mark 成cts_synthesized ,这个就是它的dont_touch 的reason

你可以get_attribute [get_nets $net] dont_touch_reasons

然后用 list_dont_touch_type 去查看dont touch的原因的意思。

这个应该就能解决你dont_touch的原因了

你好!我按照你的方法找到dont_touch_reasons是cts_synthesized,具体解释就是Net is synthesized with clock tree synthesis。我想去掉dont_touch_reasons这个属性,但是提示static or derived attribute不能去掉。怎么能把这个属性去掉让工具自动修呢?

LZ 你好 这个是做完CTS必要的这个dont_touch 属性, 为了防止data path的优化引擎去改动clock tree。但是并不会影响CTS的engine去修复与优化,所以你在CTS之后一般不会去掉, 而是如果发现没有这个属性 ,需要mark上去。当然也是有方法可以remove掉的 ,通过 mark_clock_tree这个command,具体请看man page。

mark这个dont_touch的属性,也是需要这个command。

你的树里的clk单元是多大?

还有transition设的多大?

transition time设为1ns,max_fanout没有设置,工具默认为2000吧

clkbuf单元是多大的?

没有专门的clkbuff,用的是buffda,尺寸大概是22*14u

我懂您的意思了,所以cts_synthesized属性还是保留比较好。工具对max_fanout修不了可能是因为它没有办法改变clock tree的结构,只能修改buff的大小和位置,是这样吗?

只有这一种buf么?换一个驱动能力大的试试。

你的transition 1ns,我觉得随便做做问题不大,但是你的这个buf,应该是最大驱动能力就是15,所以换个大驱动能力的完全搞定。你试试看

dont touch 为true的时候 才是dont touch

compile_clock_tree 默认应该吧你DRC 修复的 ,有变量可以控制optimize_clock_tree 也可以修复DRC。

先看看你的setting对不对吧 。如果有gate cell 你可以试试split_clock_net

你好!我在cts用的是icc student guide里的三个命令:1 clock_opt -no_clock_route -only_cts2 clock_opt -only_psyn -no_clock_route -area_recovery

3 route_zrt_group -all_clock_nets -reuse_existing_global_route true -stop_after_global_route true。

请问这个三个命令与compile_clock_tree有什么区别?我在optimize_clock_tree之前已经set_fix_hold [all_clocks],优化后还是有min_cap violations,这个violation在PT里也有,会对版图有影响吗?谢谢!

我自己的理解,不对的地方请指正。compile_clock_tree就是建立时钟树的,也可以对reset等对skew有要求,建立buf tree ,clock_opt是个打包的命令。可以cts cto extract rc route

LZ placement之前,为了工具不插入buf,dont touch的属性不能去吧?在cts前去掉比较合适吧

嗯,我在CTS之前都是带着dont_touch的,在cts的时候好像也是有dont_touch的,不过ICC在CTS的时候好像可以ignore dont_touch。我记得是在哪见过这个说明的

都是高手

是的,我lab guide上也看到了,compiler_clock_tree可以ignore dont touch的属性,clock_opt倒是没有看到有这方面的说明