IO pad 本身过DRC的错误,无语了!求助前辈!

时间:10-02

整理:3721RD

点击:

TSMC018的IO pad,DRC的时候出现以下错误:ESD.24g { @ The minimum width of RPO on drain side (X) for 5V,3.3V, 2.5V, 1.8V and 1.5V NMOS and PMOS.

@ 1.8V and 1.5V NMOS when used as power clamp device>=1.95um

X = ((ENSD_WCO OR EPSD_WCO ) AND ESD2DMY) AND RPO

Y = EGTE COIN OUTSIDE EDGE X

Z = RPO COIN INSIDE EDGE X

ENC Y Z < 1.95 ABUT < 90 REGION

}

ESD.25g { @ The minimum clearance from poly edge to CO edge on source side for NMOS and PMOS (Except ESD.26g)>=0.5um

X = ECOS AND ((ENMOS OR EPMOS ) INTERACT RPO)

EXT X EGTE_W < 0.5 ABUT < 90 OPPOSITE REGION

Y = ECO AND ESD1_NCS

EXT Y EGTE_W < 0.5 ABUT < 90 OPPOSITE REGION

}

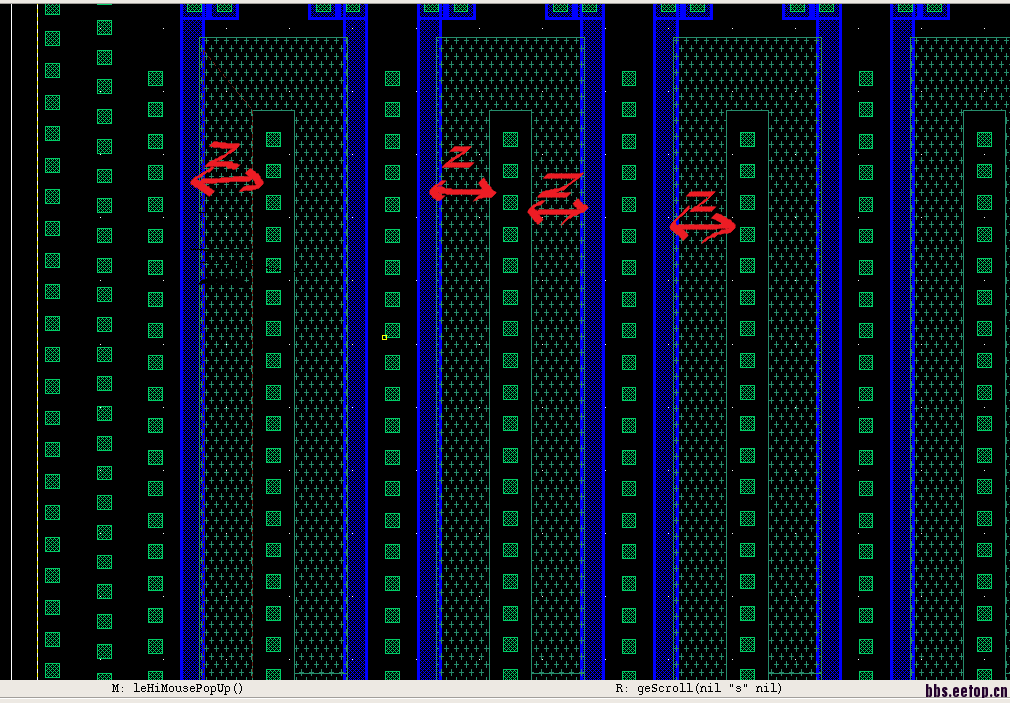

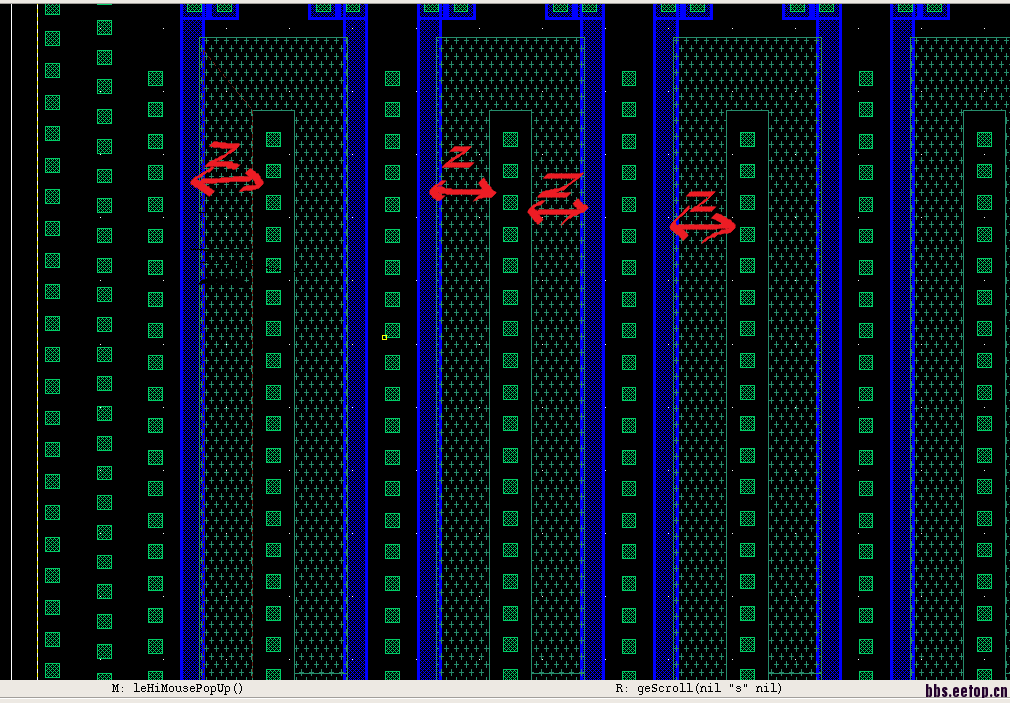

第一个图IO pad 版图,第二个为放大的只显示POLY,Contact,RPO

图中标的Z,就是出错的地方。我量了下,IO pad里面他们之间的距离不到0.8um,而DRC规则却要求之间距离大于1.95um。

这不是矛盾了吗?

求前辈指导:(1)是不是DRC有问题?若果是,这个问题是不是就可以忽略了(我不能去动pad吧)

(2)如果DRC没问题,那到底是哪里错了?我在包含这些IO pad的版图里面,过DRC同样出现很多这些错误(和单独过一个pad的DRC结果一样)

求前辈帮帮忙!多谢了!

@ 1.8V and 1.5V NMOS when used as power clamp device>=1.95um

X = ((ENSD_WCO OR EPSD_WCO ) AND ESD2DMY) AND RPO

Y = EGTE COIN OUTSIDE EDGE X

Z = RPO COIN INSIDE EDGE X

ENC Y Z < 1.95 ABUT < 90 REGION

}

ESD.25g { @ The minimum clearance from poly edge to CO edge on source side for NMOS and PMOS (Except ESD.26g)>=0.5um

X = ECOS AND ((ENMOS OR EPMOS ) INTERACT RPO)

EXT X EGTE_W < 0.5 ABUT < 90 OPPOSITE REGION

Y = ECO AND ESD1_NCS

EXT Y EGTE_W < 0.5 ABUT < 90 OPPOSITE REGION

}

第一个图IO pad 版图,第二个为放大的只显示POLY,Contact,RPO

图中标的Z,就是出错的地方。我量了下,IO pad里面他们之间的距离不到0.8um,而DRC规则却要求之间距离大于1.95um。

这不是矛盾了吗?

求前辈指导:(1)是不是DRC有问题?若果是,这个问题是不是就可以忽略了(我不能去动pad吧)

(2)如果DRC没问题,那到底是哪里错了?我在包含这些IO pad的版图里面,过DRC同样出现很多这些错误(和单独过一个pad的DRC结果一样)

求前辈帮帮忙!多谢了!

esd guideline 可以ignore,具体看io release notes,或者问tsmc

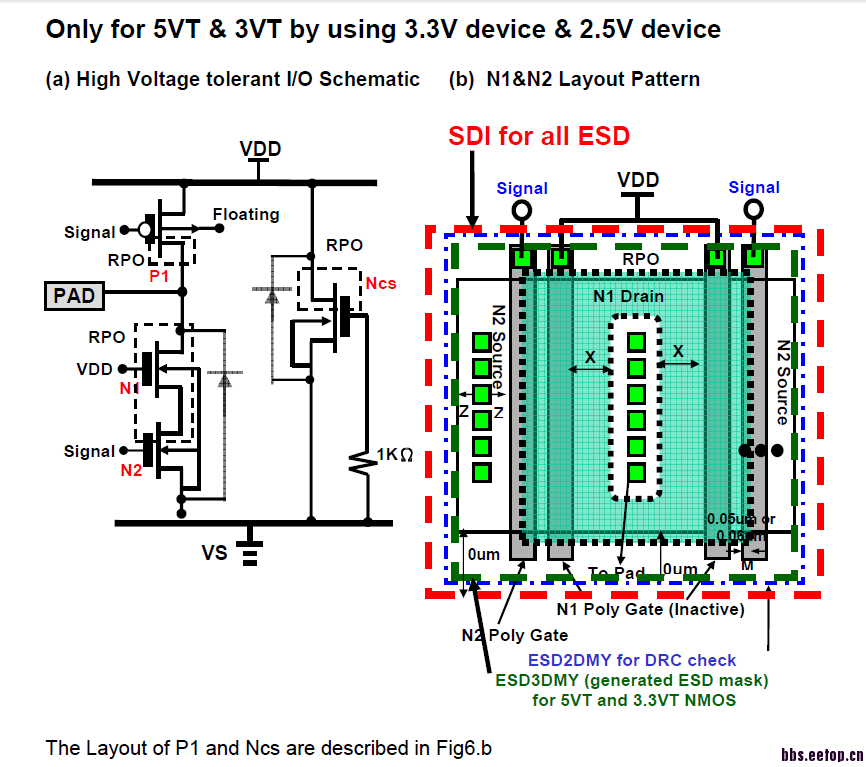

在手册里面,关于这个DRC确实是这样描述的。这下面是它的示意图,要求pad的设计那个X值(就是我帖子里面的那个手画的Z值)就是要大于1.95um的。可是实际的pad却不是这样的,是不是这个关于pad的库太差劲了。?

顶!

感觉跟你的IO 排布和电源域有关,check 一下 一个域里面有没有一个power up PAD cell

多谢您的指导!问题应经解决了,正如小编所讲的,这些错误可以忽略。在release note 里面注明的,刚开始没认真看。

多谢!

小编,问一下,你这个IO版图是在哪里找到?tsmc提供的文件里叫什么名字啊?

工艺里面自带的,看你的工作电压了

这是基于电压检查的DRC rule

先确定IO的工作电压是不是在DRC rule检查的范围内