请教一个SIP带来的时序问题

时间:10-02

整理:3721RD

点击:

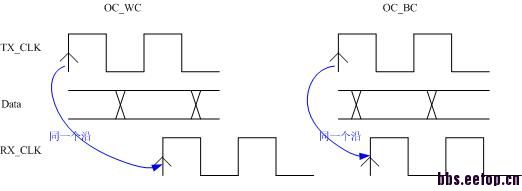

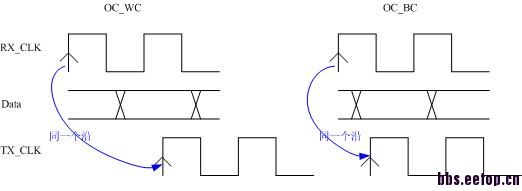

如图,某种封装中,数据端口的Data数据路径要比穿过两颗芯片的输出CLK路径短很多,如图所示,

逻辑上,TX 的第一个CLOCK沿变成了采样沿,(数据端口传输的是连续的数据信息)

我的疑惑和想法是

1 如果保证先开clock,后开数据流,虽然TX是用同一个沿采样,但应该没有逻辑问题。

2 如图是BC和WC的情况,因为时钟路径比Data长很多,我还需要额外考虑哪些因素来使得时序更加保险?

第一图TX RX标反了,编辑没删成功,请看第二幅图

那你就只有在芯片外部也就是PCB上做人为的延时了, 数据线比时钟线长一点, 但是要控制好长度

这个是在SIP内部,时序已经固定,没得补救做,但是感觉逻辑上没什么问题,

不知道大家怎么看

我对这个问题的答案很感兴趣 。