数字模块制成schematic后仿真疑问

时间:10-02

整理:3721RD

点击:

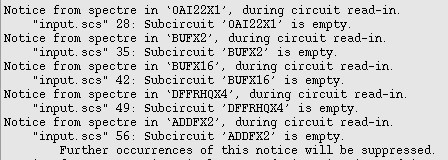

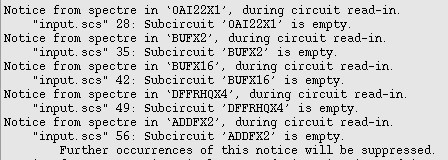

小弟的数字模块A做完数字流程后制成schematic和layout后,在cadence里用电源电压直接加测试激励,即整个电路图都属于模拟电路了。但进行仿真时模块的输出全为0,我查看log文件发现有如下警告。

但如果A的schematic激励如果用verilog编程来加的话,即建立数模混合仿真环境的话,它就能正常输出。请问这是哪儿出了问题?请教各位大大。

但如果A的schematic激励如果用verilog编程来加的话,即建立数模混合仿真环境的话,它就能正常输出。请问这是哪儿出了问题?请教各位大大。

为啥要这样做后仿呢?!不都是抽取版图的spice参数做后仿的吗?

你的意思是加sdf文件进行后仿真?这样的后仿真通过了,但我想用模拟仿真的方法去分析波形,因为我的是数控振荡器,想分析下它的输出波形的抖动。

这个我都是用calibre抽取spice参数用hspice仿的·····

你是怎么转成schematic? 打开看看是不是晶体管级的schematic。

从log看,还是调用标准单元库啊

你好,我从schematic进入下一层之后能看到所有调用的数字标准单元,再往标准单元进去之后就能看到晶体管基本的电路。我是按照数字流程来做的,做成版图后再通过.v文件和数字库生成的schematic。