verilog编程出现问题,新人求解

时间:10-02

整理:3721RD

点击:

主程序

module fdivision(f1,rst,f2);

input f1,rst;

output f2;

reg f2;

reg [7:0]j;

always @(posedge f1)

if(!rst)

begin

f2<=0;

j<=0;

end

else

begin

if(j==19)

begin

f2<=!f2;

j<=0;

end

else j<=j+1;

end

endmodule

测试程序

`timescale 1ns/100ps

`include "./fdivision.v"

`define clk 50

module fdivision_tb;

reg f1,rst;

always #`clk f1=~f1;

initial

begin

rst=1;

f1=0;

#100 rst=0;

#100 rst=1;

#10000 $stop;

end

fdivision m(

.f1(f1),

.rst(rst),

.f2(f2)

);

endmodule

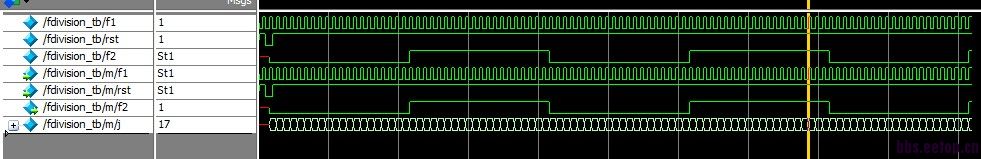

波形里f2一直是0,这是为什么呢?

唔……——||

我仿真怎么这样呢。

module fdivision(f1,rst,f2);

input f1,rst;

output f2;

reg f2;

reg [7:0]j;

always @(posedge f1)

if(!rst)

begin

f2<=0;

j<=0;

end

else

begin

if(j==19)

begin

f2<=!f2;

j<=0;

end

else j<=j+1;

end

endmodule

测试程序

`timescale 1ns/100ps

`include "./fdivision.v"

`define clk 50

module fdivision_tb;

reg f1,rst;

always #`clk f1=~f1;

initial

begin

rst=1;

f1=0;

#100 rst=0;

#100 rst=1;

#10000 $stop;

end

fdivision m(

.f1(f1),

.rst(rst),

.f2(f2)

);

endmodule

波形里f2一直是0,这是为什么呢?

[img][/img]你代码没问题啊,我放在f2会跳变的![img]{0@GLGH.jpg[/img]

唔……——||

我仿真怎么这样呢。

问题解决了^^

是不是仿真时间太短了rst还没有复位?