请教一个latch时序问题

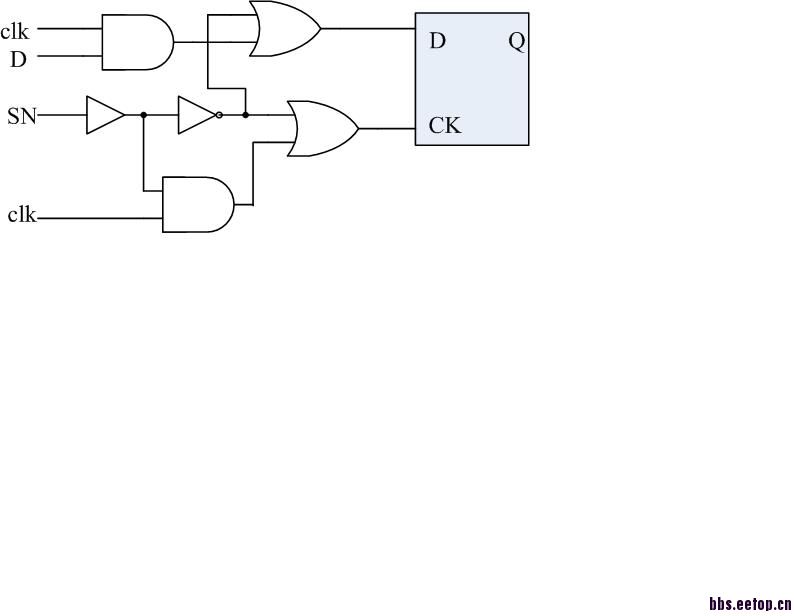

图中的SN端为置位信号,clk是时钟信号,不知道这里的约束该如何设置了?

SN端和时钟端变化都会使得后面的latch有setup和hold的时序通路,请教一下这里改如何处理,谢谢

1-是需要异步置位还是同步置位?图上的电路是异步置位

2-如果需要异步,而且你只有异步复位的触发器,建议你在rtl中,把那个信号latch_sig改成latch_sig_bar信号,这样latch_sig_bar就是异步复位了。然后加个非来控制后面的信号。

这样rtl上一点小改动就行了吧?

不是完全明白你的意思,感觉你只是解决的初值的问题,正常CK情况下的Q端值没有考虑(这个Q是不反相的)

我的意思是如下

代码是这样写的:

always@(clk or D or SN)

begin

if(!SN) Q = 1‘b1;

else if(clk) Q = D;

end

这个置位是异步的,而且设计中需要SN置位的初值1,且SN释放以后clk没变高是需要保持这个初值1

标准单元库中只提供了低电平复位的latch,且复位的初值为0,所以逻辑上要想得到置位为1的latch,只能在latch的前端CK和D端加逻辑了,这样时序就复杂了

// METHOD1

latch sig(.CK(clk),.D(data),.Q(q_out),.SN(set_n));

// METHOD2

latch_n sig_n(.CK(clk),.D(data_n),.Q(q_n),.RN(set_n));

inv inv1(.A(q_n),.Z(q_out));

inv inv2(.A(data),.Z(data_n));

//其中:

//latch是异步置位的latch

//latch_n 是异步复位的latch

以上的METHOD1与METHOD2的逻辑等价吗?

好久不做前端了,一起研究研究:)

等价的,可以采用,我已经用上了,谢谢

如果还有一个既有置位和复位的latch,好像就没办法了,

现在我只能把它改成DFF(带置位和复位)