功能仿真和综合后仿真不一致,差一个时钟周期

时间:10-02

整理:3721RD

点击:

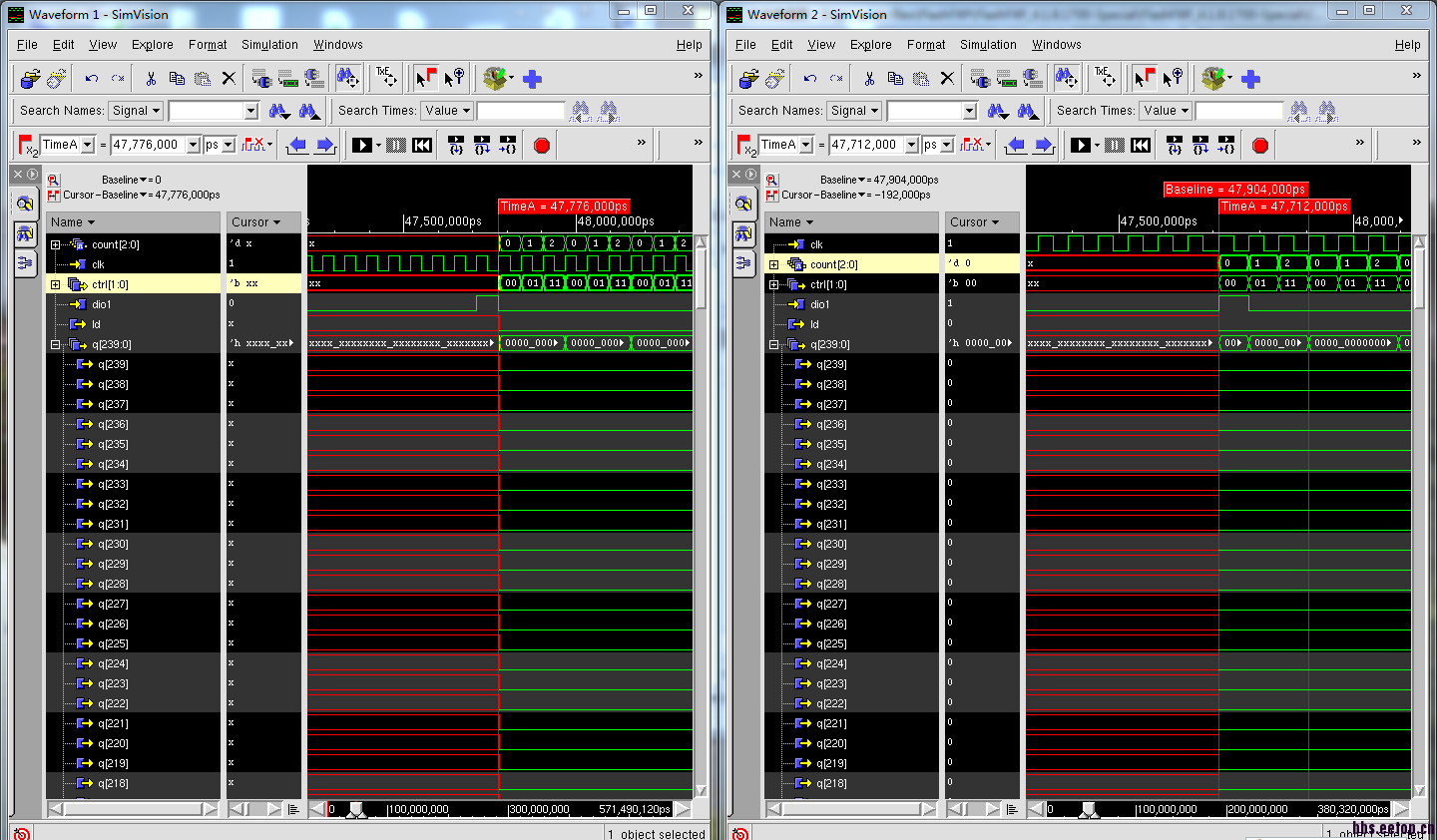

今天写了一个移位寄存器的代码,发现功能仿真和综合后的仿真差了一个周期:

module shiftreg0123(ctrl,ld,q,clk,dio1);

input clk;

input dio1;

output[239:0] q;

output ld;

output[1:0] ctrl;

reg[239:0] q;

reg ld;

reg[1:0] count;

reg[1:0] ctrl;

always @ (posedge clk) // shift data 1

begin

if(dio1==1||count==2)

begin

count<=0;

ld<=q[239];

q<=(q<<1);

q[0]<=dio1;

ctrl<=2'b00; //r

end

else

begin

count<=count+1;

if(ctrl==2'b00)

ctrl<=2'b01; //g

else if(ctrl==2'b01)

ctrl<=2'b11;//b

else

ctrl<=2'b00; //r

end

end

endmodule

本来是在DIO1这个信号变为1时开始移位的,综合后成了DIO1变为0时开始移位,差了一个周期。是因为我写的代码不太合格吗?

自己顶一下,先写个小模块再测试下