generate语句,DC综合会报错,是什么原因

时间:10-02

整理:3721RD

点击:

verilog写法:

generatebeginif(PARAMETER1)begin

a =……;

b =……;

end

else begin

a =……;

b =……;

end

endendgenerate

DC 报错 syntax error on a obsolute verilog 2001 construct standalone generate block (VER-946)

请高手指点

没有 assign,没有always,你这段代码是写在哪里的?

DC支持generate,建议好好看看语法~

reg类型是不需要assign的,我说的是generate block,不是说always block,我没说compile有问题的,我说的是DC综合报Error基本常识一般人都懂得,翻书就能解决的语法问题是没必要拿到网上来问的,亲!

跟你吵架就没意思了,generate block不能独立于assign、always block和单元例化 存在...wire a,b;

......

generate

......

assign a=....

assign b=....

......

assign a=....

assign b=....

......

我只想说,你在强调的事情,根本不是解决问题的关键!你这写法,也是报错的,不信就自己试一下!

DC肯定是有某些设定或者限制,具体的ERROR编号我已经贴在那了,我只是想知道那个ERROR INFO代表什么意思

小编那样写 好像是可以的 这样用类似于用define

小编要注意的是 把未选择的代码去掉 看一下该文件内整个代码是否连贯,语法是否正确

最好的办法还是用vcs或者nc先仿一遍

nc/vcs 和simulation结果完全正常,代码规则检查也没有任何问题,就是到了DC这里报错

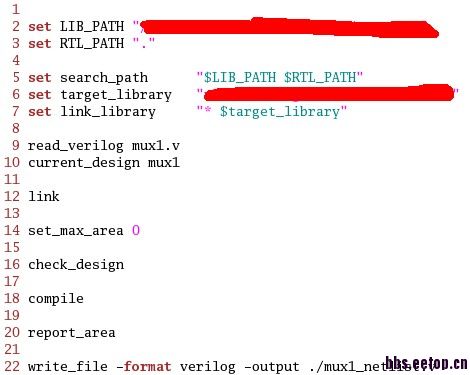

读入时,是用read_verilog 还是 analyze+elabrate

貌似前者是选用parameter的缺省值,不能传参的。

我试没问题。

DC脚本

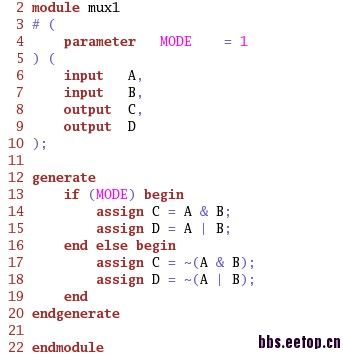

verilog文件

试试

set hdlin_vrlg_std 2001