dc和pt下report_timing同一路径的delay不同的问题

时间:10-02

整理:3721RD

点击:

求助

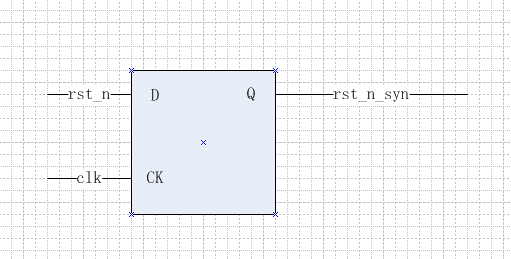

某一路径原理图如下:

功能很简单,将外部的rst_n信号打进clk,然后得到rst_n_syn,作为复位送到电路中其余寄存器的RB端。

pt下分析的是pre route的时序,虽然知道这个分析没有把保持时间修正,但问题不在这。

在dc中的约束和pt的约束全部相同,给rst_n加了set_ideal_network -no_propagate rst_n

rst_n的inputdelay认为是clk域下的0 delay。

在dc下报告report_timing -delay min

发现从reg/CK到reg/Q端时间为0.6ns

在pt下报告同样的timing

发现从reg/CK到reg/Q的时间为0ns。

如果我将pt中的约束去掉set_ideal_network -no_propagate rst_n。那么pt下这个路径的CK到Q的timing就和dc结果一直。

为何同样的约束在dc和pt下的report_timing时序不一样?

为何set_ideal_network(在pt下)在寄存器的D端会对Ck到Q的timing acrs产生影响?

帮顶。

可能还有其他的不同吧

set_ideal_network设置的rst_n

同学

是不是搞错了啊。

?能详细说下么?是我这里的表述错了,还是我的设置错了,不应该把rst_n定义为ideal network么?我的目的是希望dc下不优化rst_n的线网,交给pr去做即可

想不优化的话,你直接false path掉不就好了么,效果也差不多

false_path 只能对时序的问题做不优化,但是如果是drv的问题,还是会有buffer