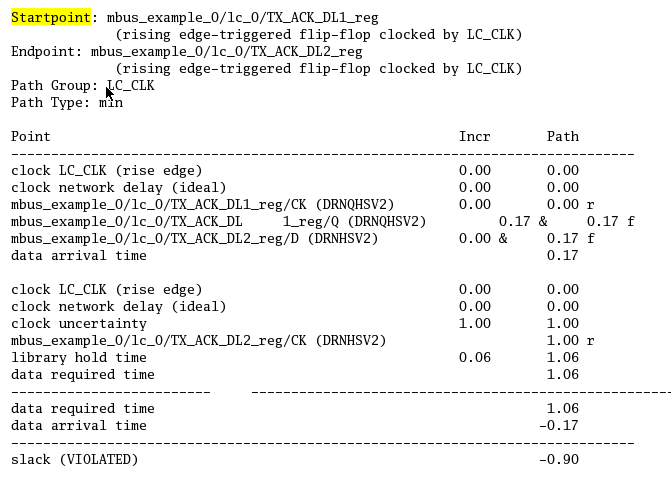

求助!PT分析的报告如图,为啥跟ICC的不一样,路径是一样的。

时间:10-02

整理:3721RD

点击:

ICC的报告是符合的,而且没有了clock uncertainly 这一项 所以就符合了,并且用的sdc文件是一样的,都是1的clock uncertainly。请教怎么回事?

RE: 求助!PT分析的报告如图,为啥跟ICC的不一样,路径是一样的。

以PT的结果为准。你的PT用的网表是ICC之后的吗?图里clock network delay都是ideal,delay为0这是有问题的,按理说ICC做完CTS之后network delay不应该为0,也不是ideal。感觉ICC没有考虑clock uncertainty,要是考虑的话会在这条路径上插BUF以满足hold呀

你这个PT报告不对,做了CTS之后clock network delay不应该是ideal,在pt里设置set_propagated_clock再检查timing。

sdc要使用ICC吐出来的吧,而且你的clock还是ideal的

用的是ICC的网表,network delay 那ideal 是因为没有加上set_propagated_clock指令,加上后就不是ideal 也不是0了,这个问题昨天解决了。现在我就是纳闷,为什么ICC的时序报告中没有clock uncertainty这一项,而我做的PT中有这一项。以至于他们的ICC时序报告是符合的,而我这边PT报告时违反的。先谢过大神了

我不是大神。一般跑ICC的时候算timing都会考虑clock_uncertainty的呀。你看是每个步骤的timing report都没有考虑还是只有某个步骤没考虑。你在各个步骤的脚本中都设置一下clock_uncertainty