时序优化,用Timing Debug分析时序后,接着怎样操作才能使时序满足

时间:10-02

整理:3721RD

点击:

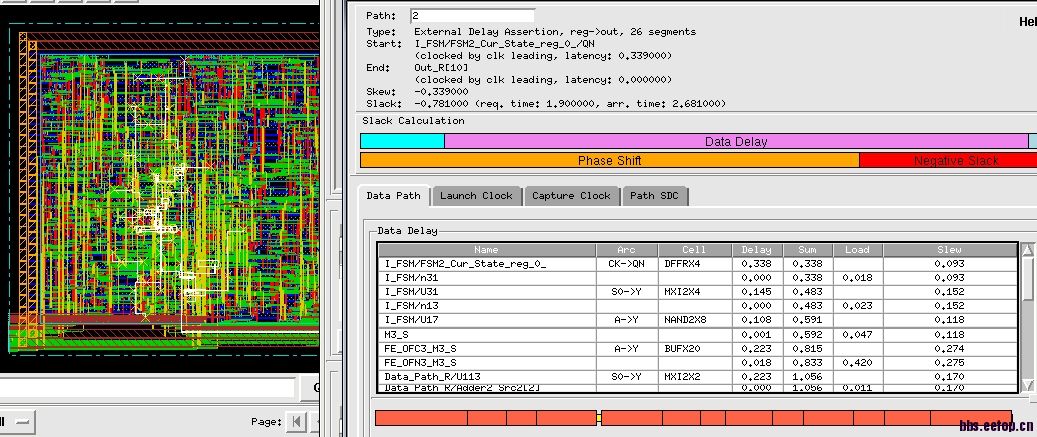

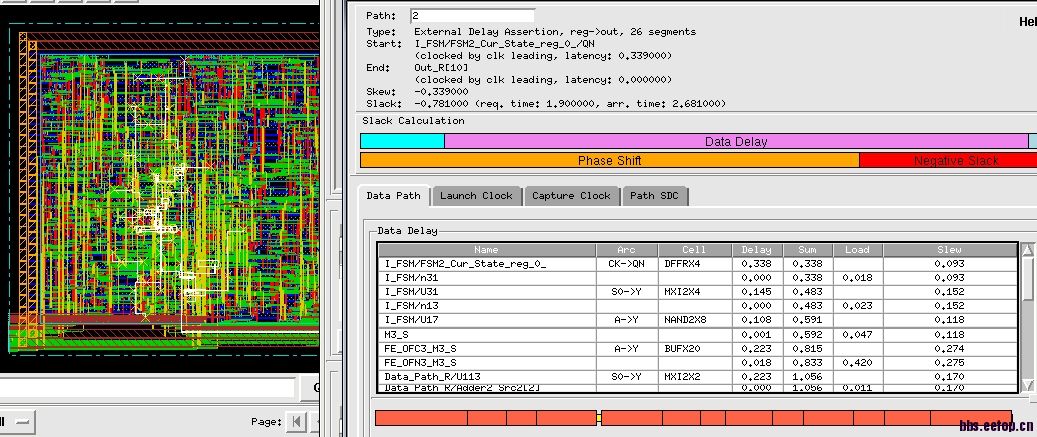

在post-route后进行了optDesign -postRoute优化,时序还是不收敛,WNS = -0.784ns,违反路径条数158条。接着采用Timing Debug分析时序,做到“Using Categories to Analyze Timing Results”如下图所示。

,

,

到这里后请问如何进行下去,是通过查看那个门的延时比较长,然后将其调换为驱动能力大些的门来降低延时,最终使时序满足。请问各位大侠是这样的吗?

,

,到这里后请问如何进行下去,是通过查看那个门的延时比较长,然后将其调换为驱动能力大些的门来降低延时,最终使时序满足。请问各位大侠是这样的吗?

可以试试

1)optDesign 两到三遍

2)重新floorplan,把那个ff放到output port附近

3)看output delay设置是否合理

我用了optDesign 好几遍时序没什么变化,也重新floorplan,都没什么效果。现在用ceoChangeCell,改变单元的尺寸有了些改善,但是不大,现在正在调试中。请问涛哥这样做对吗?

你这个模块也不大,我看图怎么感觉你的port都挤在一起了,都挤在左下角了?

是的,这是一个课程设计。pin我也调整过间距和位置,结果好像还要差些

如果让encounter自己决定所有port的位置,可以得到较好的timing。

按照你给的信息,没有太多的建议了。除非提供更加详细的内容,比如,

1)这条path的详细timing report,以及相应的物理位置(cell和net),以便分析路径是否合理,哪里可以改进。

2)所有时序违反path的timing report,看看是否有哪些group有共同的问题

这些是根据经验,见招拆招的做法,没有太多固定的规律。跟有经验的学长学习的就是这些东西

今天回过头来看自己发的帖子,以前真的什么也不懂。涛哥讲了那么多有用的东西当时却一点也没领会到,这说明学习是需要过程的,在此感谢涛哥对小弟的指导。